# 用户手册

# APM32F030x6x8xC

基于 Arm® Cortex®-M0+内核的 32 位微控制器

版本: V2.3

# 目录

| 1   | 简介及文档描述规则       | 6  |

|-----|-----------------|----|

| 1.1 | 简介              | 6  |

| 1.2 | 文档描述规则          | 6  |

| 2   | 系统架构            | 9  |

| 2.1 | 术语全称、缩写描述       | 9  |

| 2.2 | 系统架构框图          | 9  |

| 2.3 | 存储器映射           | 11 |

| 2.4 | 启动配置            | 11 |

| 3   | FLASH 存储器       | 13 |

| 3.1 | 术语全称、缩写描述       | 13 |

| 3.2 | 主要特征            | 13 |

| 3.3 | Flash 存储器结构     | 13 |

| 3.4 | 功能描述            | 14 |

| 3.5 | 寄存器地址映射         | 18 |

| 3.6 | 寄存器功能描述         | 19 |

| 4   | 系统配置控制器(SYSCFG) | 23 |

| 4.1 | 术语全称、缩写描述       | 23 |

| 4.2 | 寄存器地址映射         | 23 |

| 4.3 | 寄存器功能描述         | 23 |

| 5   | 复位与时钟管理(RCM)    | 29 |

| 5.1 | 术语全称、缩写描述       | 29 |

| 5.2 | 复位功能描述          | 29 |

| 5.3 | 时钟管理功能描述        | 31 |

| 5.4 | 寄存器地址映射         | 38 |

| 5.5 | 寄存器功能描述         | 39 |

| 6   | 电源管理单元(PMU)     | 56 |

| 6.1 | 术语全称、缩写描述       | 56 |

| 6.2 | 简介              | 56 |

| 6.3 | 结构框图            | 56 |

| 6.4 | 功能描述            | 57 |

| 6.5 | 寄存器地址映射         | 60 |

| 6.6  | 寄存器功能描述                   | 60 |

|------|---------------------------|----|

| 7    | 嵌套向量中断控制器(NVIC)           | 62 |

| 7.1  | 术语全称、缩写描述                 | 62 |

| 7.2  | 简介                        | 62 |

| 7.3  | 主要特征                      | 62 |

| 7.4  | 中断和异常向量表                  | 62 |

| 8    | 外部中断与事件控制器(EINT)          | 64 |

| 8.1  | 简介                        | 64 |

| 8.2  | 功能描述                      | 64 |

| 8.3  | 寄存器地址映射                   | 66 |

| 8.4  | 寄存器功能描述                   | 66 |

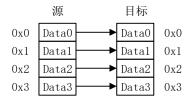

| 9    | 直接存储器存取(DMA)              | 69 |

| 9.1  | 简介                        | 69 |

| 9.2  | 主要特征                      | 69 |

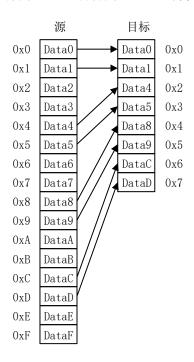

| 9.3  | 功能描述                      | 69 |

| 9.4  | 寄存器地址映射                   | 75 |

| 9.5  | 寄存器功能描述                   | 76 |

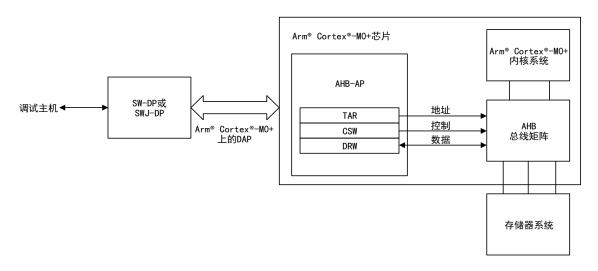

| 10   | 调试 MCU(DBGMCU)            | 80 |

| 10.1 | 术语全称、缩写描述                 | 80 |

| 10.2 | 简介                        | 80 |

| 10.3 | 主要特征                      | 80 |

| 10.4 | 功能描述                      | 81 |

| 10.5 | 寄存器地址映射                   | 81 |

| 10.6 | 寄存器功能描述                   | 81 |

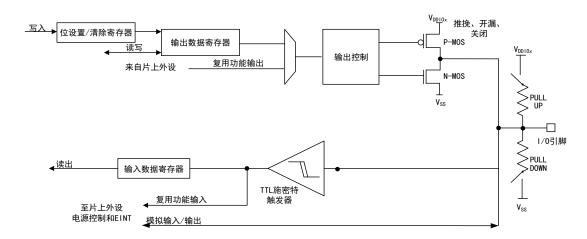

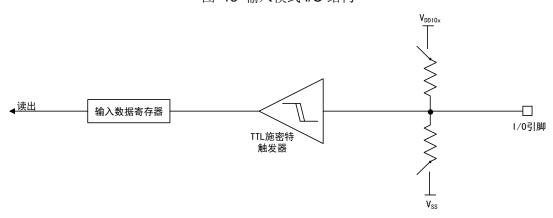

| 11   | 通用/复用功能输入/输出引脚(GPIO/AFIO) | 85 |

| 11.1 | 术语全称、缩写描述                 | 85 |

| 11.2 | 主要特征                      | 85 |

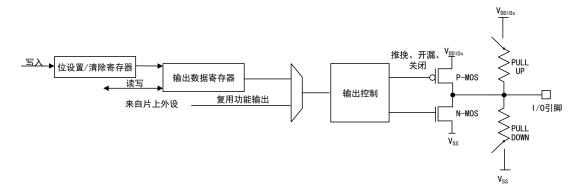

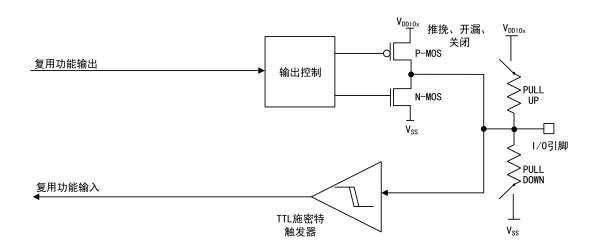

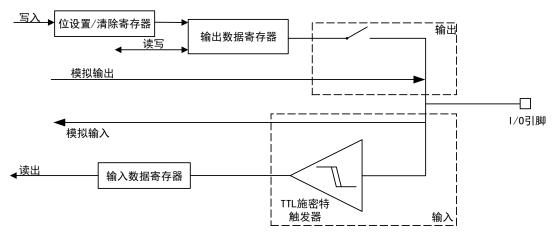

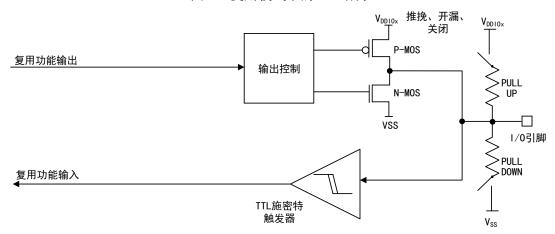

| 11.3 | 结构框图                      | 86 |

| 11.4 | 功能描述                      | 86 |

| 11.5 | 寄存器地址映射                   | 91 |

| 11.6 | 寄存器功能描述                   | 91 |

| 12   | 定时器概述                     | 96 |

| 12.1 | 术语全称、缩写描述                 | 96 |

| 12.2 | 定时器类别及主要差异            | 96  |

|------|-----------------------|-----|

| 13   | 高级定时器(TMR1)           | 99  |

| 13.1 | 简介                    | 99  |

| 13.2 | 主要特征                  | 99  |

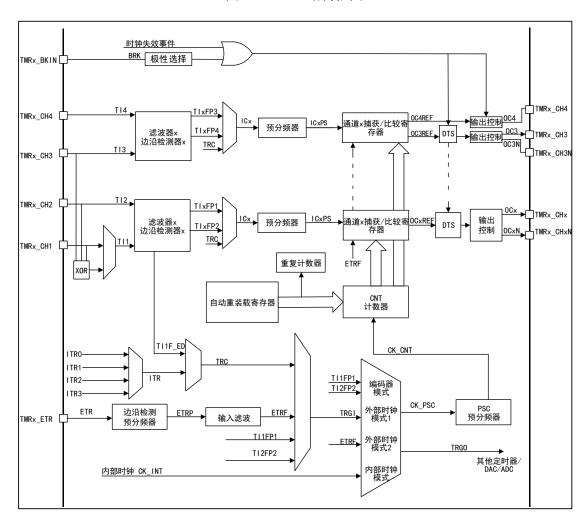

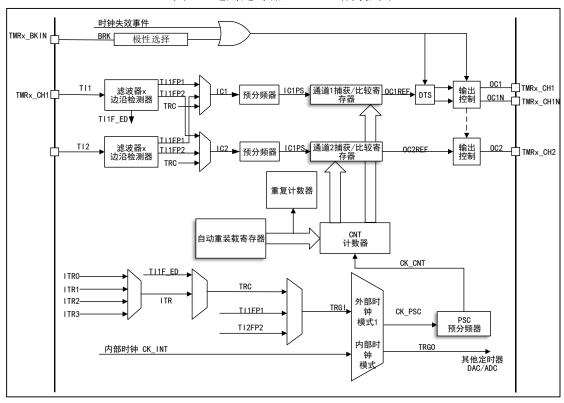

| 13.3 | 结构框图                  | 100 |

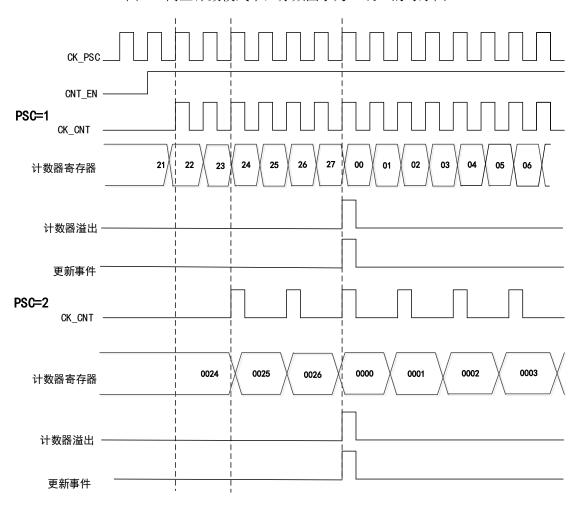

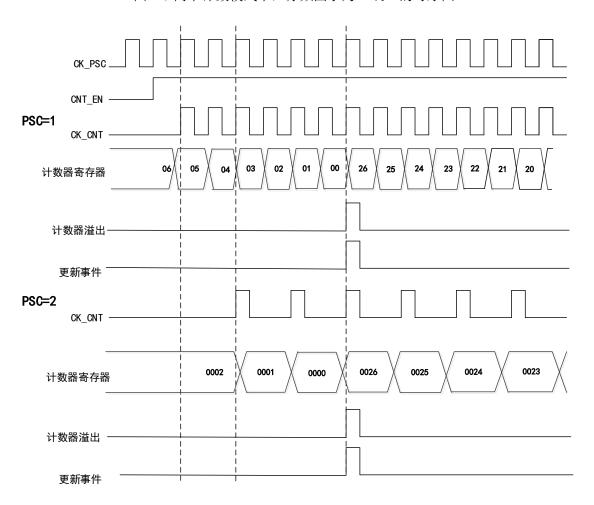

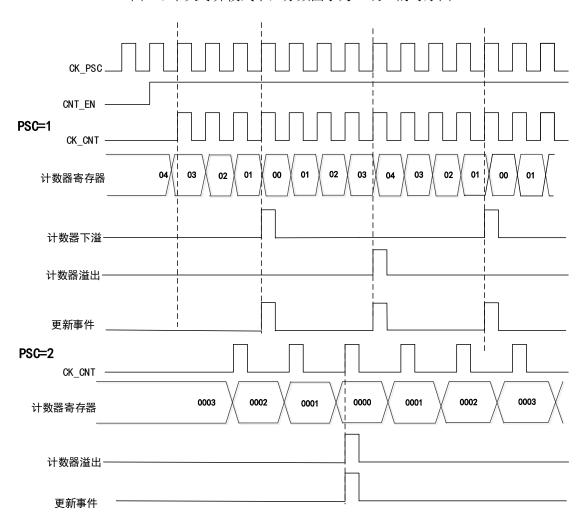

| 13.4 | 功能描述                  | 100 |

| 13.5 | 寄存器地址映射               | 116 |

| 13.6 | 寄存器功能描述               | 117 |

| 14   | 通用定时器(TMR3)           | 135 |

| 14.1 | 简介                    | 135 |

| 14.2 | 主要特性                  | 135 |

| 14.3 | 结构框图                  | 136 |

| 14.4 | 功能描述                  | 136 |

| 14.5 | 寄存器地址映射               | 149 |

| 14.6 | 寄存器功能描述               | 150 |

| 15   | 通用定时器(TMR14)          | 166 |

| 15.1 | 简介                    | 166 |

| 15.2 | 主要特性                  | 166 |

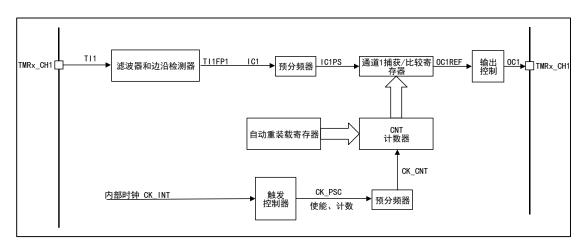

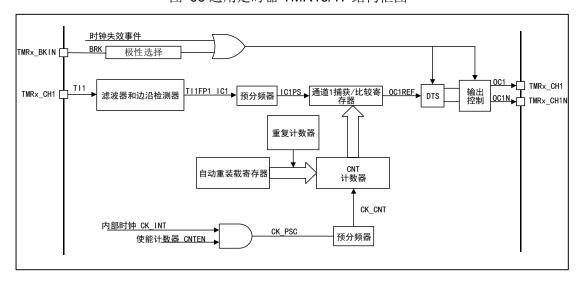

| 15.3 | 结构框图                  | 166 |

| 15.4 | 功能描述                  | 167 |

| 15.5 | 寄存器地址映射               | 170 |

| 15.6 | 寄存器功能描述               | 171 |

| 16   | 通用定时器(TMR15/16/17)    | 178 |

| 16.1 | 简介                    | 178 |

| 16.2 | 主要特性                  | 178 |

| 16.3 | 结构框图                  | 179 |

| 16.4 | 功能描述                  | 180 |

| 16.5 | TMR15 寄存器地址映射         | 189 |

| 16.6 | TMR15 寄存器功能描述         | 190 |

| 16.7 | TMR16 和 TMR17 寄存器地址映射 | 203 |

| 16.8 | TMR16 和 TMR17 寄存器功能描述 | 204 |

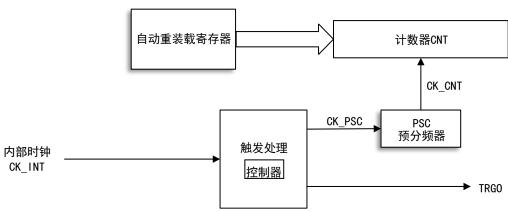

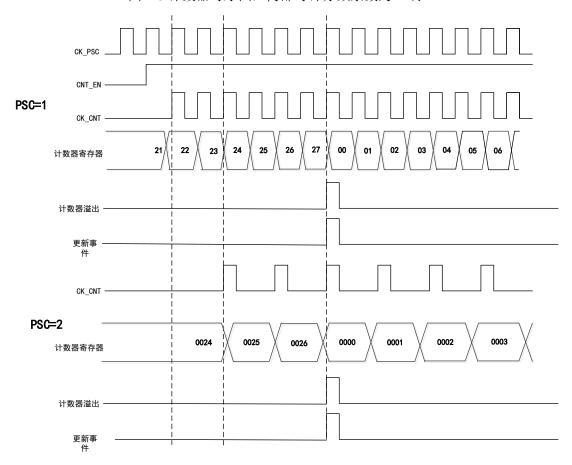

| 17   | 基本定时器(TMR6/TMR7)      | 216 |

| 17.1 | 简介                    | 216 |

| 17.2 | 主要特征                   | 216 |

|------|------------------------|-----|

| 17.3 | 结构框图                   | 216 |

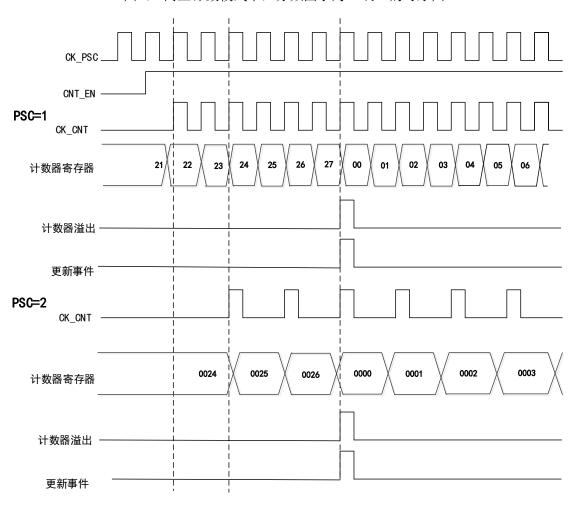

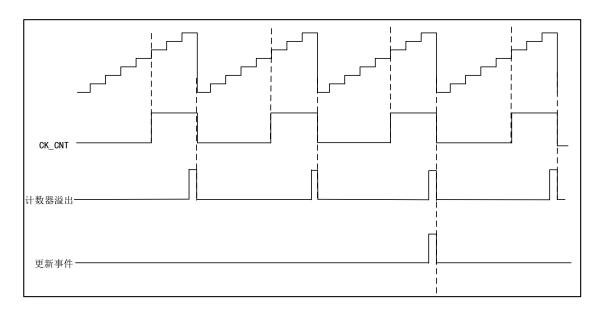

| 17.4 | 功能描述                   | 216 |

| 17.5 | 寄存器地址映射                | 218 |

| 17.6 | 寄存器功能描述                | 218 |

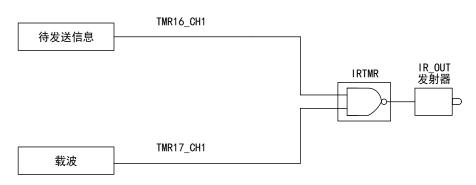

| 18   | 红外定时器(IRTMR)           | 221 |

| 18.1 | 简介                     | 221 |

| 18.2 | 功能描述                   | 221 |

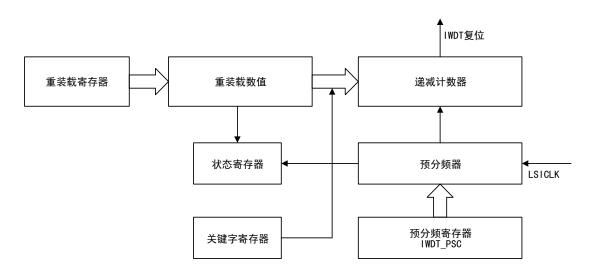

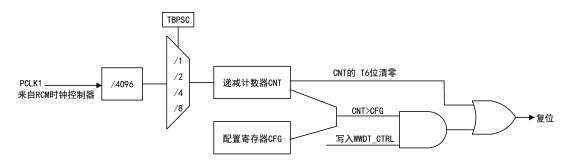

| 19   | 看门狗定时器( <b>WDT</b> )   | 222 |

| 19.1 | 简介                     | 222 |

| 19.2 | 独立看门狗                  | 222 |

| 19.3 | 窗口看门狗                  | 224 |

| 19.4 | IWDT 寄存器地址映射           | 225 |

| 19.5 | IWDT 寄存器功能描述           | 226 |

| 19.6 | WWDT 寄存器地址映射           | 228 |

| 19.7 | WWDT 寄存器功能描述           | 228 |

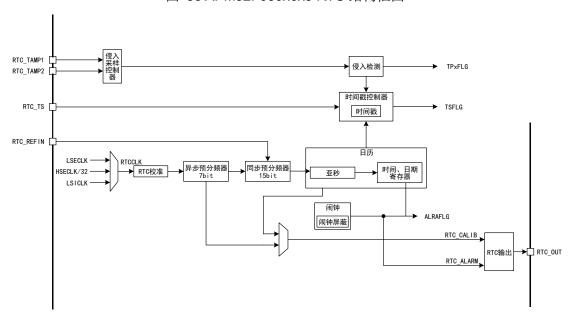

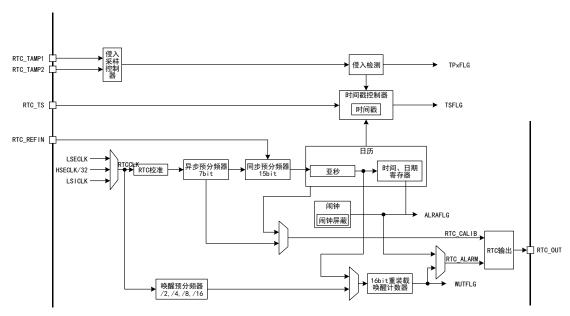

| 20   | 实时时钟(RTC)              | 230 |

| 20.1 | 术语全称、缩写描述              | 230 |

| 20.2 | 简介                     | 230 |

| 20.3 | 主要特征                   | 230 |

| 20.4 | 结构框图                   | 231 |

| 20.5 | 功能描述                   | 232 |

| 20.6 | 寄存器地址映射                | 237 |

| 20.7 | 寄存器功能描述                | 237 |

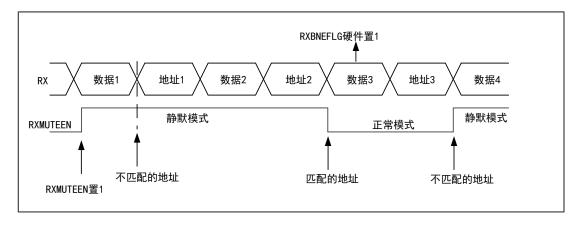

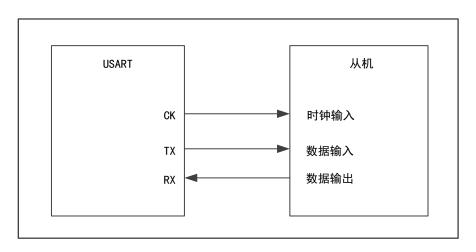

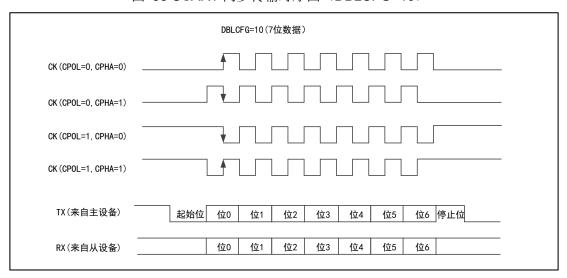

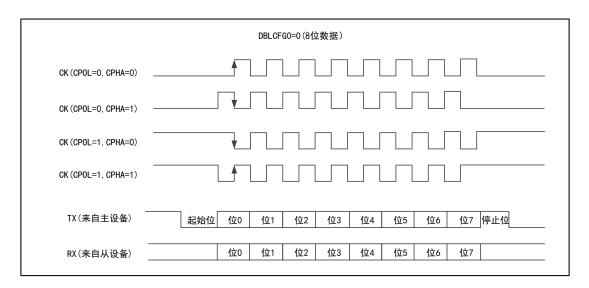

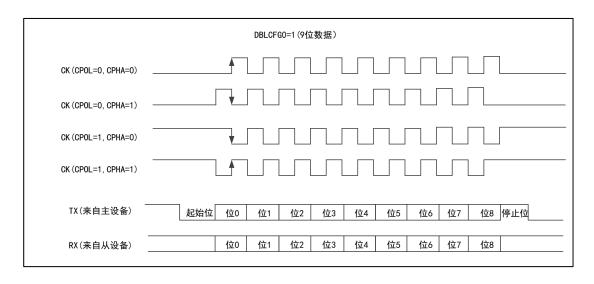

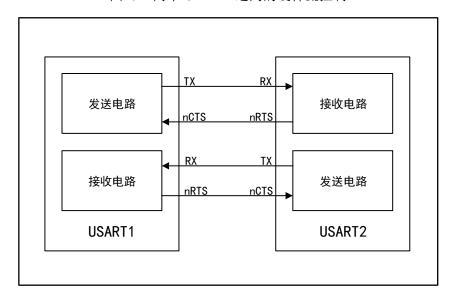

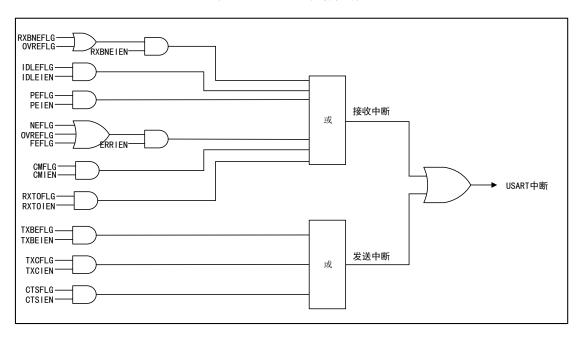

| 21   | 通用同步异步收发器(USART)       | 250 |

| 21.1 | 术语全称、缩写描述              | 250 |

| 21.2 | 简介                     | 250 |

| 21.3 | 主要特征                   | 250 |

| 21.4 | 功能描述                   | 251 |

| 21.5 | 寄存器地址映射                | 264 |

| 21.6 | 寄存器功能描述                | 264 |

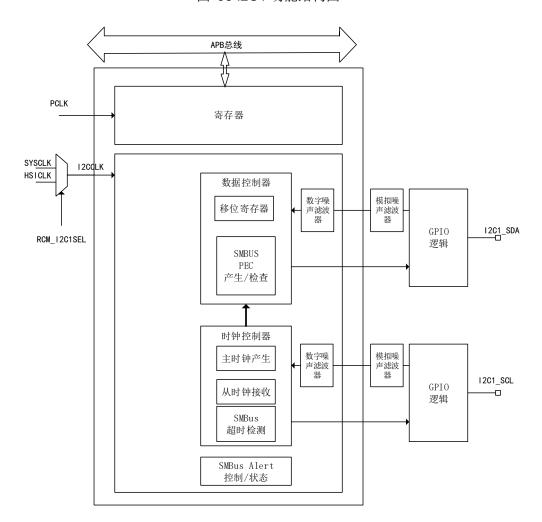

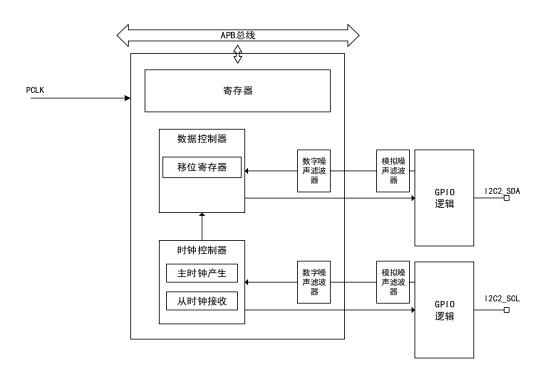

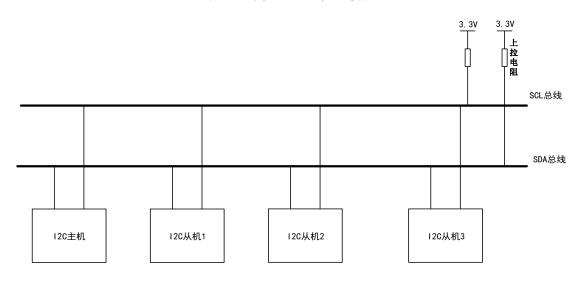

| 22   | 内部集成电路接口( <b>I2C</b> ) | 275 |

| 22.1 | 术语全称、缩写描述              | 275 |

| 22.2 | 简介                                | 275 |

|------|-----------------------------------|-----|

| 22.3 | 主要特征                              | 275 |

| 22.4 | 结构框图                              | 276 |

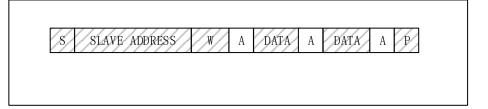

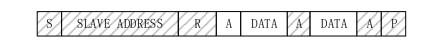

| 22.5 | 功能描述                              | 277 |

| 22.6 | 寄存器地址映射                           | 286 |

| 22.7 | 寄存器功能描述                           | 287 |

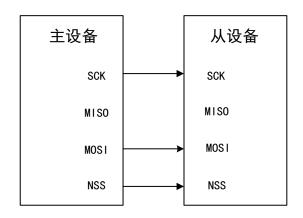

| 23   | 串行外设接口(SPI)                       | 297 |

| 23.1 | 术语全称、缩写描述                         | 297 |

| 23.2 | 简介                                | 297 |

| 23.3 | 主要特征                              | 297 |

| 23.4 | 功能描述                              | 298 |

| 23.5 | 寄存器地址映射                           | 309 |

| 23.6 | 寄存器功能描述                           | 309 |

| 24   | 模拟数字转换器(ADC)                      | 316 |

| 24.1 | 简介                                | 316 |

| 24.2 | 主要特征                              | 316 |

| 24.3 | 功能描述                              | 317 |

| 24.4 | 寄存器地址映射                           | 321 |

| 24.5 | 寄存器功能描述                           | 321 |

| 25   | 循环冗余校验计算单元(CRC)                   | 328 |

| 25.1 | 简介                                | 328 |

| 25.2 | 功能描述                              | 328 |

| 25.3 | 寄存器地址映射                           | 328 |

| 25.4 | 寄存器功能描述                           | 329 |

| 26   | 芯片电子签名(CHIP ELECTRONIC SIGNATURE) | 331 |

| 26.1 | 简介                                | 331 |

| 26.2 | 功能描述                              | 331 |

| 26.3 | 寄存器功能描述                           | 331 |

| 27   | 版本历史                              | 333 |

### 1 简介及文档描述规则

### 1.1 简介

本参考手册向应用程序开发人员提供关于如何使用 MCU (微控制器) 系统架构、存储器和外设所涉及的全部信息。

关于 Arm® Cortex®-M0+内核的相关信息,请参考 Arm® Cortex®-M0+技术参考手册,关于型号信息、尺寸和器件的电气特性等详细数据请参考对应的数据手册(Datasheet),有关 MCU 系列全部型号中,存储器映射、外设存在情况及其数目请查阅相应的数据手册。

在此说明:珠海极海半导体有限公司,在以下正文中,简称"Geehy"。

### 1.2 文档描述规则

### 1.2.1 "寄存器功能描述"规则

- (1) 控制类(CTRL)寄存器,未特别说明,都是"软件置 1 和清 0"。

- (2) 控制类寄存器后面一般会有动词缩写以作区别,动词可以有: EN-Enable、CFG-Configure、D-Disable、SET-Setup、SEL-Select

- (3) 状态类寄存器缩写后面一般会有 FLG 以作区别。

- (4) 数值、数据类寄存器,一般会包括 V、VALUE、D、DATA,这些词后面不加动词,比如:xxPSC,CNT,后面一般不添加动词。

### 1.2.2 术语全称、缩写描述

表格 1 R/W 缩写及描述

| R/W                     | 描述                                | 缩写    |

|-------------------------|-----------------------------------|-------|

| read/write              | 软件能读写此位。                          | R/W   |

| read-only               | 软件只能读此位。                          | R     |

| write-only              | 软件只能写此位,读此位将返回复位值。                | W     |

| read/clear              | 软件可以读此位,也可以通过写 1 清除此位,写 0 对此位无影响。 | RC_W1 |

| read/clear              | 软件可以读此位,也可以通过写0清除此位,写1对此位无影响。     | RC_W0 |

| read/clear by read      | 软件可以读此位,读此位将自动地清除它为0,写此位无效。       | RC_R  |

| read/set                | 软件可以读也可以设置此位,写 0 对此位无影响。 R/S      |       |

| read-only write trigger | 软件可以读此位,写0或1触发一个事件但对此位数值没有影响。     | RT_W  |

| toggle                  | 软件只能通过写 1 来翻转此位,写 0 对此位无影响。       | Т     |

表格 2 常用寄存器功能描述术语全称、缩写

| 中文全称 | 英文全称        | 英文缩写 |

|------|-------------|------|

| 使能   | Enable      | EN   |

| 禁止   | Disable     | D    |

| 清除   | Clear       | CLR  |

| 选择   | Select      | SEL  |

| 配置   | Configure   | CFG  |

| 控制   | Contrl      | CTRL |

| 控制器  | Controller  | С    |

| 复位   | Reset       | RST  |

| 停止   | Stop        | STOP |

| 设置   | Set         | SET  |

| 装载   | Load        | LD   |

| 校准   | Calibration | CAL  |

| 初始化  | Initialize  | INIT |

| 错误   | Error       | ERR  |

| 状态   | Status      | STS  |

| 准备   | Ready       | RDY  |

| 软件   | Software    | SW   |

| 硬件   | Hardware    | HW   |

| 源    | Source      | SRC  |

| 系统   | System      | SYS  |

| 外设   | Peripheral  | PER  |

| 地址   | Address     | ADDR |

| 方向   | Direction   | DIR  |

| 时钟   | Clock       | CLK  |

| 输入   | Input       | I    |

| 输出   | Output      | 0    |

| 中断   | Interrupt   | INT  |

| 数据   | Data        | DATA |

| 大小   | Size        | SIZE |

| 除法器  | Divider     | DIV  |

| 预分频器 | Prescaler   | PSC  |

| 乘法器  | Multiplier  | MUL  |

| 中文全称 | 英文全称   | 英文缩写 |

|------|--------|------|

| 周期   | Period | PRD  |

### 表格 3 模块全称、简写

| 中文全称        | 英文全称                                                    | 英文缩写    |

|-------------|---------------------------------------------------------|---------|

| 复位与时钟管理     | Reset and Clock Management                              | RCM     |

| 电源管理单元      | Power Management Unit                                   | PMU     |

| 嵌套向量中断控制器   | Nested Vector Interrupt Controller                      | NVIC    |

| 外部中断/事件控制器  | External Interrupt /Event Controller                    | EINT    |

| 直接存储器存取     | Direct Memory Access                                    | DMA     |

| 调试 MCU      | Debug MCU                                               | DBG MCU |

| 通用输入/输出引脚   | General-Purpose Input Output Pin                        | GPIO    |

| 复用功能输入/输出引脚 | Alternate Function Input Output Pin                     | AFIO    |

| 定时器         | Timer                                                   | TMR     |

| 看门狗定时器      | Watchdog Timer                                          | WDT     |

| 独立看门狗       | Independent Watchdog Timer                              | IWDT    |

| 窗口看门狗       | Windows Watchdog Timer                                  | WWDT    |

| 实时时钟        | Real-Time Clock                                         | RTC     |

| 通用同步异步收发器   | Universal Synchronous Asynchronous Receiver Transmitter | USART   |

| 内部集成电路接口    | Inter-integrated Circuit Interface                      | I2C     |

| 串行外设接口      | Serial Peripheral Interface                             | SPI     |

| 片上音频接口      | Inter-IC Sound Interface                                | I2S     |

| 模拟数字转换器     | Analog-to-Digital Converter                             | ADC     |

| 循环冗余校验计算单元  | Cyclic Redundancy Check Calculation Unit                | CRC     |

# 2 系统架构

# 2.1 术语全称、缩写描述

表格 4 术语全称、缩写描述

| 中文全称    | 英文全称                          | 英文缩写 |

|---------|-------------------------------|------|

| 高级高性能总线 | Advanced High-Performance Bus | AHB  |

| 高级外围总线  | Advanced Peripheral Bus       | APB  |

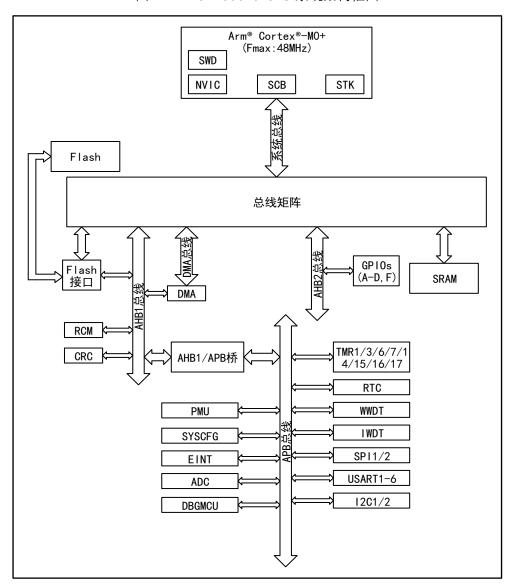

### 2.2 系统架构框图

主系统主要由两个主模块和四个从模块构成。主模块分别是 Arm® Cortex®-M0+内核和通用 DMA。从模块分别是内部 SRAM、内部闪存存储器 FLASH、连接所有 GPIO 口的 AHB2 总线和在 AHB1 总线上的 AHB1/APB 桥,其中,AHB1/APB 桥连接所有外设设备。

这些都是通过一个多级的 AHB 总线构架相互连接的,如下图所示:

图 1 APM32F030x6x8xC 系统架构框图

注: APM32F030x6x8 没有 USART3-6, 且没有 TMR7。

表格 5 总线名称

| 名称           | 说明                                               |  |

|--------------|--------------------------------------------------|--|

| 系统总线         | 连接 Arm® Cortex®-M0+内核的系统总线(外设总线)与总线矩阵。           |  |

| DMA 总线       | 连接 DMA 的 AHB 主控接口与总线矩阵。                          |  |

|              | 协调内核和 DMA 的访问;由 CPU AHB、系统总线、DMA 总线和 FMC、SRAM、   |  |

| 总线矩阵         | AHB2 和 AHB1/APB 桥组成。AHB 外设通过总线矩阵与系统总线相连,允许 DMA 访 |  |

|              | 问。                                               |  |

| AHB/APB 桥    | 桥在 AHB 和 APB 总线间提供同步连接。                          |  |

| AIID/AFD 10F | 当对 APB 寄存器进行非 32 位访问时,访问会被自动转换成 32 位。            |  |

### 2.3 存储器映射

存储器映射地址总共是 4GB 地址,分配的地址包括内核(包括内核外设)、片上 Flash(包括主存储区、系统存储区、选项字节)、片上 SRAM、总线外设(包括 AHB、APB 外设),各类地址具体信息请参考对应型号的数据手册。

### 2.3.1 嵌入式 SRAM

内置静态 SRAM。它可以以字节、半字(16 位)或全字(32 位)访问。SRAM 的起始地址是 0x2000 0000。

### 2.4 启动配置

APM32F 微控制器系列实现了一个特殊的机制,通过配置 BOOT0 引脚参数和 FMC\_OBCS 中的 nBOOT1 位,可以用有三种不同的启动模式,即系统可以不仅 仅从 Flash 存储器或系统存储器启动,还可以从内置 SRAM 启动。被选作启动区域的存储器是由选择的启动模式决定的。

| 启动模式选择引脚 |       | 启动模式              | <del>计图文字</del>                                              |

|----------|-------|-------------------|--------------------------------------------------------------|

| BOOT1    | воото | <b>万</b>          | 访问方式                                                         |

| Х        | 0     | 主闪存存储器<br>(Flash) | 主闪存存储器被映射到启动空间,但仍然能够<br>在它原有的地址访问它,即闪存存储器的内容<br>可以在两个地址区域访问。 |

| 0        | 1     | 系统存储器             | 系统存储器被映射到启动空间(0x0000 0000),但仍然能够在它原有的地址访问它。                  |

| 1        | 1     | 内置 SRAM           | 只能在开始的地址区访问 SRAM。                                            |

表格 6 启动模式配置及其访问方式

### 注意:

- (1) 启动空间地址为 0x0000 0000

- (2) Flash 原有地址为 0x0800 0000

- (3) F030x6x8 产品的系统存储器原有地址为 0x1FFF EC00; F030xC 产品的系统存储器原有地址 为 0x1FFF D800

- (4) SRAM 的起始地址为 0x2000 0000

- (5) BOOT1 的值为 nBOOT1 选项位取反

用户可以通过设置 BOOT1(配置 nBOOT1)和 BOOT0 引脚的状态,来选择在复位后的启动模式。 BOOT 引脚应在待机模式下保持用户需要的启动配置,当从待机模式退出时,引脚的值会被锁存。 如果选择从内置 SRAM 启动,那么在编写应用代码时,必须使用 NVIC 的异常表和偏移寄存器,重新将向量表映射至 SRAM 中。

### 空片检测功能

该功能仅适用于 APM32F030xC 产品。

当 BOOTO 引脚设置为主闪存存储器时,使用该功能。当 BOOTO 引脚设置为系

统存储器时,可以对主闪存存储器进行编程。

该功能仅在选项字节加载期间更新,如果 Flash 地址 0x08000000 内容为 0xFFFFFFF,即系统处于无程序状态,将会进入 BootLoader。且该功能只有在 当下次上电检测或者设置 FMC\_CTRL2 寄存器的 OBLOAD 位时,才会更新。

### 内嵌的启动程序

内嵌的启动程序由 Geehy 在生产线上写入并存放在系统存储区域。

# 3 Flash 存储器

本章主要介绍 Flash 的存储结构、读、擦、写、读/写保护、解锁/锁定特性,及涉及到的寄存器功能描述。

### 3.1 术语全称、缩写描述

表格 7 术语全称、缩写描述

| 中文全称     | 英文全称                    | 英文缩写 |

|----------|-------------------------|------|

| 闪存存储器控制器 | Flash Memory Controller | FMC  |

### 3.2 主要特征

- (1) Flash 存储器结构

- 分为主存储区、信息块

- 主存储区容量最高为 256KB

- 信息块分为系统存储区、选项字节

- 系统存储区存放 BootLoader 程序、96 位唯一 UID、主存储区容量信息,容量大小:

- APM32F030x6x8 为 3KB

- APM32F030xC 为 8KB

- 选项字节区容量大小为 16Bytes

#### (2) 功能说明

- 读取 Flash

- 页/片擦 Flash

- 写 Flash

- 读/写保护 Flash

- 配置选项字节

## 3.3 Flash 存储器结构

表格 8 APM32F030x6x8 系列产品 Flash 存储结构

| 块    | 名称 地址区域 |                           | 大小 (字节) | 扇区           |

|------|---------|---------------------------|---------|--------------|

| 主存储区 | 页 0     | 0x0800 0000 - 0x0800 03FF | 1K      |              |

| 主存储区 | 页 1     | 0x0800 0400 - 0x0800 07FF | 1K      | 扇 0          |

| 主存储区 | 页 2     | 0x0800 0800 - 0x0800 0BFF | 1K      | /44 <b>U</b> |

| 主存储区 | 页 3     | 0x0800 0C00 - 0x0800 0FFF | 1K      |              |

| 主存储区 | •••     |                           | •••     | •••          |

| 主存储区 | 页 28    | 0x0800 7000 - 0x0800 73FF | 1K      | 扇 7          |

| 主存储区 | 页 29    | 0x0800 7400 - 0x0800 77FF | 1K      | )44 <b>/</b> |

| 块    | 名称 地址区域 |                           | 大小 (字节) | 扇区      |

|------|---------|---------------------------|---------|---------|

| 主存储区 | 页 30    | 0x0800 7800 - 0x0800 7BFF | 1K      |         |

| 主存储区 | 页 31    | 0x0800 7C00 - 0x0800 7FFF | 1K      |         |

| 主存储区 | •••     |                           | •••     | •••     |

| 主存储区 | 页 60    | 0x0800 F000 - 0x0800 F3FF | 1K      |         |

| 主存储区 | 页 61    | 0x0800 F400 - 0x0800 F7FF | 1K      | 扇 15    |

| 主存储区 | 页 62    | 0x0800 F800 - 0x0800 FBFF | 1K      | /43/ TO |

| 主存储区 | 页 63    | 0x0800 FC00 - 0x0800 FFFF | 1K      |         |

| 信息块  | 系统存储区   | 0x1FFF EC00 - 0x1FFF F7FF | 3K      | -       |

| 信息块  | 选项字节    | 0x1FFF F800 - 0x1FFF F80F | 16      | -       |

注: APM32F030x6x8 系列产品的主存储块包含页(扇)的数量和具体产品的 Flash 容量有关。

表格 9 APM32F030xC 系列产品 Flash 存储结构

| 块    | 名称    | 地址区域                      | 大小 (字节) | 扇区                  |

|------|-------|---------------------------|---------|---------------------|

| 主存储区 | 页 0   | 0x0800 0000 - 0x0800 07FF | 2K      | 良 0                 |

| 主存储区 | 页 1   | 0x0800 0800 - 0x0800 0FFF | 2K      | 扇 0                 |

| 主存储区 | •••   |                           | •••     | •••                 |

| 主存储区 | 页 62  | 0x0801 F000 - 0x0801 F7FF | 2K      | 良 24                |

| 主存储区 | 页 63  | 0x0801 F800 - 0x0801 FFFF | 2K      | 扇 31                |

| 主存储区 | •••   | •••                       | •••     | •••                 |

| 主存储区 | 页 126 | 0x0803 F000 - 0x0803 F7FF | 2K      | 扇 64                |

| 主存储区 | 页 127 | 0x0803 F800 - 0x0803 FFFF | 2K      | / <sub>3</sub> 3 04 |

| 信息块  | 系统存储区 | 0x1FFF D800 - 0x1FFF F7FF | 8K      | -                   |

| 信息块  | 选项字节  | 0x1FFF F800 - 0x1FFF F80F | 16      | -                   |

### 3.4 功能描述

描述对主存储器、信息块(包括系统存储区、选项字节)的操作,包括读、写、擦、读/写保护。

读取 Flash 包括主存储块、信息块,擦、写、读/写包括分开介绍;系统存储区在出厂时已写入,用户无法修改,不介绍该模块的擦、写、读/写保护。

### 3.4.1 读取 Flash

Flash 存储器可直接寻址,读取 Flash 受以下配置影响:

### 等待周期

针对不同的系统时钟需配置不同的等待周期:

- 0 个等待周期: 0<系统时钟≤24MHz

- 1 个等待周期: 24MHz<系统时钟≤48MHz

#### 预取缓存区

可提高读取速度,每次复位预取缓存区被自动打开;带预取缓存的读接口;只有系统时钟和 AHB 时钟一致、系统时钟小于 24MHz 时才能配置,系统时钟和 AHB 时钟一致时才能使用。

#### 半周期访问

在需要优化功耗时可使用半周期访问;此时系统时钟和 AHB 时钟一致,且系统时钟为 8MHz 或低于 8MHz 才能使用半周期访问 Flash,否则必须处于开启状态。

### 3.4.2 主存储块

#### 3.4.2.1 擦主存储块

FMC 支持页擦除和整片擦除(全擦除)两种方式将主存储区的内容初始化为高电平(数据表现为 0xFFFF)。用户在对 Flash 进行写入前,建议对写入地址页先进行擦除操作,若写入地址的数据不是 0xFFFF 则会触发一个编程错误。

#### 主存储器页擦除

页擦除是根据程序选择的主存储区页进行独立擦除,不会对未选择擦除的页产生 任何影响。

正确的页擦除(或闪存写入操作)结束后,FMC\_STS 寄存器的 OCF 将会被置位,若开启了 OCIE 中断则将触发一个操作完成中断。用户需要注意的是选择擦除的页必须是有效的页(主存储区有效的地址和未被写保护的地址)。

#### 主存储器片擦除

片擦除操作将会使 Flash 主存储区内所有内容全部被擦除,用户在使用时需要特别注意,以避免误操作导致重要数据丢失。

#### 3.4.2.2 写主存储块

FMC 支持对主存储区的 16 位(半字)数据写入,可选择通过 Debug、BootLoader、程序在 SRAM 中运行、直接读取已擦除的页等方式判断是否擦除成功。

为保证写入正确,需要在写入前检查目的地址是否已经被擦除,若未被擦除,则写入数据无效并将 FMC\_STS 寄存器的 PEF 位置"1"。若目的地址存在写保护,则写入数据无效并触发一个写保护错误(FMC STS 的 WPEF 位置"1")。

### 3.4.2.3 读/写保护主存储块

闪存读/写保护用以防止非法读出/修改主存储区代码或数据,它由选项字节的读/

写保护配置字节控制。对于 APM32F030x6x8xC 系列产品,写保护的基本单位是 4 页(即 4KBytes)。

#### 读保护

读保护有三个级别,分布是:等级 0、等级 1、等级 2,具体情况如下:

表格 10 读保护级别区别

| 类别   | READPROT               | 描述                                                                                      |

|------|------------------------|-----------------------------------------------------------------------------------------|

| 等级 0 | 0xAA                   | 主存储区、选项字节可擦、写、读。                                                                        |

| 等级 1 | 除了 0xAA 和<br>0xCC 的其它值 | 用户模式:允许对主存储区、选项字节擦、写、读。 Debug、SRAM 运行、系统储存区运行:禁止访问主存储区;选项字节可擦、写、读,但当等级修改为0时,会先执行主存储区片擦。 |

| 等级 2 | 0xCC                   | 无法 Debug,对主存储区、选项字节无法擦、写、读,等级也无法修改。                                                     |

### 写保护

可通过配置写保护选项字节 WRP0/1/2/3 的值来实现对主存储块对应的页进行写保护控制,写保护开启后,主存储区对应页的内容使用任何方式都不能被修改。

#### 3.4.2.4 解锁/锁定主存储块

复位后 FMC 的 FMC\_CTRL1 会被硬件锁定,此时不能直接对 FMC\_CTRL1 进行写入操作,必须先按照正确的顺序向 FMC\_KEY 写入对应的值来解锁 FMC。 KEY 值如下:

- KEY1=0x45670123

- KEY2=0xCDEF89AB

错误的写入顺序或错误的值均会使程序进入硬件错误,而且此时 FMC 将被锁定,所有 FMC 操作均无效,直到下次复位才能解除。用户也可以通过向控制寄存器 2(FMC CTRL2)的 LOCK 位写"1"来软件锁定 FMC。

用户在每次 Flash 编程操作中必须按照 "Flash 解锁一用户编程一 Flash 上锁"的步骤进行,以避免在 Flash 编程操作结束后,因 Flash 未上锁而带来的用户代码/数据被意外修改等风险。

### 3.4.3 选项字节

### 3.4.3.1 擦选项字节

支持擦除功能,正确的选项字节擦除(或选项字节写入操作)结束后, FMC\_STS 寄存器的 OCF 将会被置位,若开启了 OCIE 中断使能则将触发一个操 作完成中断。

#### 3.4.3.2 写选项字节

选项字节的8个可配置字节均支持写入功能。

#### 3.4.3.3 写保护选项字节

默认状态下,选项字节始终是可以读且被写保护。要想对选项字节块进行写操作(编程/擦除)首先要在 FMC\_OBKEY 中写入正确的键序列(与上锁时一样),随后允许对选项字节块的写操作,FLASH\_CTRL2 寄存器的 OBWEN 位标示允许写,清除这位将禁止写操作。

#### 3.4.3.4 解锁/锁定选项字节

系统复位后选项字节默认处于锁定状态,只有进行正确的解锁操作才能修改选项字节。选项字节解锁与闪存解锁不同点在 KEY 值写入的是 FMC\_OBKEY 寄存器而不是 FMC\_KEY 寄存器。选项字节不支持"软件上锁",用户需要特别注意的是每次修改选项字节的值后,需要系统复位才能使之生效。

### 3.4.4 选项字节功能描述

选项字节为用户提供了一些可供选择的功能,它主要由 8 个可配置的字节和对应的补码组成。在每次系统复位后,选项字节区将被重加载到 FMC\_OBCS 和 FMC\_WRTPROT 寄存器(选项字节只有每次被重加载到 FMC 后中才会生效)。在重加载过程中,若出现某个可配置字节与它的反码不匹配问题,则将触发一个选项字节错误(FMC\_寄存器的 OBE 位置"1"),同时这个字节将会被置为"0xFF"。选项字节区 16 字节的信息见下表。

表格 11 选项字节

| 地址          | 选项字节      | 初始值  | R/W | 功能描述                                                                                                                                                                                                                                                                                                                                    |

|-------------|-----------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1FFF F800 | READPROT  | 0xA5 | R/W | 读保护配置<br>位[7:0]: READPROT<br>0xAA: 等级 0<br>0xCC: 等级 2<br>其它: 等级 1                                                                                                                                                                                                                                                                       |

| 0x1FFF F801 | nREADPROT | 0x5A | R   | READPROT 补码                                                                                                                                                                                                                                                                                                                             |

| 0x1FFF F802 | UOB       | 0xFF | R/W | 用户选项字节<br>位 0: WDTSEL<br>0: 硬件看门狗<br>1: 软件看门狗<br>位 1: nRSTSTOP<br>0: 进入 Stop 模式时产生复位<br>1: 进入 Stop 模式时不产生复位<br>位 2: nRSTSTB<br>0: 进入 Standby 模式时产生复位<br>1: 进入 Standby 模式时产生复位<br>位 3: 保留<br>位 4: nBOOT1<br>选择 BOOT 模式<br>位 5: VDDAMONI<br>0: VDDA 供电检测器禁止<br>1: VDDA 供电检测器使能<br>位 6: SRAMPARITY<br>0: RAM 的奇偶校验检查禁止<br>1: RAM 的奇偶校验检查使能 |

| 地址          | 选项字节   | 初始值  | R/W | 功能描述     |

|-------------|--------|------|-----|----------|

|             |        |      |     | 位 7: 保留  |

| 0x1FFF F803 | nUOB   | 0x00 | R   | UOB 补码   |

| 0x1FFF F804 | Data0  | 0xFF | R/W | 用户数据字节 0 |

| 0x1FFF F805 | nData0 | 0x00 | R   | Data0 补码 |

| 0x1FFF F806 | Data1  | 0xFF | R/W | 用户数据字节 1 |

| 0x1FFF F807 | nData1 | 0x00 | R   | Data1 补码 |

| 0x1FFF F808 | WRP0   | 0xFF | R/W | 写保护配置 0  |

| 0x1FFF F809 | nWRP0  | 0x00 | R   | WRP0 补码  |

| 0x1FFF F80A | WRP1   | 0xFF | R/W | 写保护配置 1  |

| 0x1FFF F80B | nWRP1  | 0x00 | R   | WRP1 补码  |

| 0x1FFF F80C | WRP2   | 0xFF | R/W | 写保护配置 2  |

| 0x1FFF F80D | nWRP2  | 0x00 | R   | WRP2 补码  |

| 0x1FFF F80E | WRP3   | 0xFF | R/W | 写保护配置 3  |

| 0x1FFF F80F | nWRP3  | 0x00 | R   | WRP3 补码  |

注意: 当可配置字节和它的反码值为"0xFF"时,重加载过程中将不会再进行匹配验证

表格 12 主存储区写保护 WRPx 功能描述

| 产品容量             | 功能描述                                                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| APM32F030x6 系列产品 | WRPx 中的每一个 bit 位控制主存储区 4KB(4 页)地址的写保护<br>0: 开启写保护<br>1: 未开启写保护<br>WRP0: 第 0-31 页                                                            |

| APM32F030x8 系列产品 | WRPx 中的每一个 bit 位控制主存储区 4KB(4 页)地址的写保护<br>0: 开启写保护<br>1: 未开启写保护<br>WRP0: 第 0-31 页<br>WRP1: 第 32-63 页                                         |

| APM32F030xC 系列产品 | WRPx 中的第 0~30 位,其中每个 bit 位控制主存储区 4KB(2 页)地<br>址的写保护,第 31 位控制主存储区 132KB 地址的写保护<br>0: 开启写保护<br>1: 未开启写保护<br>WRP0: 第 0-31 页<br>WRP1: 第 32-63 页 |

注意: Flash 读/写保护配置是互相独立的,解除写保护不会强制丢失主存储区的内容,而是原样保留。

### 3.5 寄存器地址映射

基地址: 0x40022000

表格 13 FMC 寄存器地址映射

| 寄存器名        | 描述           | 偏移地址 |

|-------------|--------------|------|

| FMC_CTRL1   | 控制寄存器 1      | 0x00 |

| FMC_KEY     | 关键字寄存器       | 0x04 |

| FMC_OBKEY   | 选项字节寄存器      | 0x08 |

| FMC_STS     | 状态寄存器        | 0x0C |

| FMC_CTRL2   | 控制寄存器 2      | 0x10 |

| FMC_ADDR    | 闪存地址寄存器      | 0x14 |

| FMC_OBCS    | 选项字节控制/状态寄存器 | 0x1C |

| FMC_WRTPROT | 写保护寄存器       | 0x20 |

# 3.6 寄存器功能描述

### 3.6.1 控制寄存器 1 (FMC\_CTRL1)

偏移地址: 0x00 复位值: 0x0000 0000

| 位/域  | 名称   | 名称 R/W 描述 |                                        |  |  |       |

|------|------|-----------|----------------------------------------|--|--|-------|

|      |      |           | 配置等待周期(Wait State Configure)           |  |  |       |

| 2:0  | WS   | R/W       | 000: 0 个等待周期,0<系统时钟≤24MHz              |  |  |       |

| 2.0  | WS   | FX/VV     | 001: 1 个等待周期,24MHz<系统时钟≤48MHz          |  |  |       |

|      |      |           | 其他:保留                                  |  |  |       |

| 3    | 保留   |           |                                        |  |  |       |

|      |      |           | 使能预取缓存区(Prefetch Buffer Enable)        |  |  |       |

| 4    | PBEN | R/W       | 0: 禁用                                  |  |  |       |

|      |      |           |                                        |  |  | 1: 使能 |

|      |      |           | 预取缓存区状态标志(Prefetch Buffer Status Flag) |  |  |       |

| 5    | PBSF | R         | 0: 处于关闭状态                              |  |  |       |

|      |      |           | 1: 处于打开状态                              |  |  |       |

| 31:6 |      |           | 保留                                     |  |  |       |

# 3.6.2 关键字寄存器 1(FMC\_KEY)

偏移地址: 0x04 复位值: xxxx xxxx

| 位/域  | 名称  | R/W | 描述                                                                  |

|------|-----|-----|---------------------------------------------------------------------|

| 31:0 | KEY | W   | FMC 关键字(FMC Key)<br>写入这些位所表示的关键字可以解锁 FMC,这些位只能执行写操作,执行<br>读操作时返回 0。 |

### 3.6.3 选项字节关键字寄存器(FMC\_OBKEY)

偏移地址: 0x08 复位值: xxxx xxxx

| 位/域  | 名称    | R/W | 描述                                                                                |

|------|-------|-----|-----------------------------------------------------------------------------------|

| 31:0 | OBKEY | W   | 选项字节关键字(Option Byte Key)<br>写入这些位所表示的关键字可以解除选项字节写操作的锁定,这些位只能<br>执行写操作,执行读操作时返回 0。 |

# 3.6.4 状态寄存器 (FMC\_STS)

偏移地址: 0x0C

复位值: 0x0000 0000

| 位/域  | 名称                                                                   | R/W                                                                      | 描述                                                        |  |  |

|------|----------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| 0    | BUSYF                                                                | R                                                                        | 忙碌标志(Busy Flag)<br>该位表示正在进行闪存操作,这些位只能执行写操作,执行读操作时返回<br>0。 |  |  |

| 1    |                                                                      |                                                                          | 保留                                                        |  |  |

| 2    | PEF                                                                  | ### PEF R/W 编程错误标志(Programming Error Flag)                               |                                                           |  |  |

| 3    |                                                                      | 保留                                                                       |                                                           |  |  |

| 4    | WPEF                                                                 | WPEF R/W 写保护错误标志(Write Protection Error Flag) 当编程 FLASH 里写保护地址时,该位由硬件置位。 |                                                           |  |  |

| 5    | OCF R/W 操作完成标志(Operation Complete Flag)<br>当 FLASH 里的读/写操作完成时,由硬件置位。 |                                                                          |                                                           |  |  |

| 31:6 | 保留                                                                   |                                                                          |                                                           |  |  |

# 3.6.5 控制寄存器 2 (FMC\_CTRL2)

偏移地址: 0x10

复位值: 0x0000 0080

| 位/域 | 名称                                                                | R/W | 描述                                               |  |

|-----|-------------------------------------------------------------------|-----|--------------------------------------------------|--|

| 0   | PG                                                                | R/W | 编程(Program)<br>该位置 1 进行 Flash 编程操作。              |  |

| 1   | PAGEERA                                                           | R/W | 页擦除(Page Erase)<br>该位置 1 进行页擦除。                  |  |

| 2   | MASSERA                                                           | R/W | 整片擦除(Mass Erase)<br>该位置 1 进行整片擦除。                |  |

| 3   | 保留                                                                |     |                                                  |  |

| 4   | OBP R/W 编程选项字节(Option Byte Program)<br>该位置 1 进行选项字节编程操作。          |     |                                                  |  |

| 5   | OBE R/W 擦除选项字节(Option Byte Erase)<br>该位置 1 进行选项字节擦除操作。            |     |                                                  |  |

| 6   | STA R/W 开始进行擦除操作(Start Erase)<br>该位只能由软件置 1,在 STS_BUSYF 位清 0 时复位。 |     |                                                  |  |

| 7   | LOCK                                                              | R/W | 锁定(Lock)<br>该位只能写 1,该位置 1 表示 FMC 和 CTRL2 寄存器被锁定。 |  |

| 8   | 保留                                                                |     |                                                  |  |

| 位/域   | 名称         | R/W | 描述                                                                                            |  |

|-------|------------|-----|-----------------------------------------------------------------------------------------------|--|

| 9     | OBWEN      | R/W | 使能选项字节写操作(Option Byte Write Enable)<br>当该位置 1 时,选项字节可以被编程。                                    |  |

| 10    | ERRIE      | R/W | 使能错误中断(Error Interrupt Enable) 0: 禁止中断 1: 使能中断 当 STS_PEF=1 或 STS_WPEF=1 时,设置该位产生中断。           |  |

| 11    | 保留         |     |                                                                                               |  |

| 12    | OCIE R/W 1 |     | 使能操作完成中断(Operation Complete Interrupt Enable) 0: 操作完成中断禁用 1: 操作完成中断使能 当 STS_OCF=1 时,设置该位产生中断。 |  |

| 13    | OBLOAD R/W |     | 强制选项字节加载(Force Option Byte Load)<br>该位置 1 时,强制选项字节重装载,生成系统复位。<br>0:闲置<br>1:强制加载               |  |

| 31:14 | 保留         |     |                                                                                               |  |

### 3.6.6 地址寄存器(FMC\_ADDR)

偏移地址: 0x14

复位值: 0x0000 0000

该寄存器由硬件修改为当前/最后使用的地址;页擦除时,需通过软件配置该寄存器。

| 位/域  | 名称   | R/W | 描述                                                                |  |  |

|------|------|-----|-------------------------------------------------------------------|--|--|

| 31:0 | ADDR | W   | Flash 地址(Flash Address)<br>在进行编程操作时,该位写入要编程的地址,在进行页擦除时,该位写入要擦除的页。 |  |  |

### 3.6.7 选项字节控制/状态寄存器(FMC\_OBCS)

偏移地址: 0x1C

复位值: 0xXXXX XX0X

该寄存器的复位值与写入选项字节中的数值有关; OBE 位的复位值与加载的选项字节数值和它的反码是否一致的结果有关。

| 位/域   | 名称       | R/W | 描述                                                                                                         |

|-------|----------|-----|------------------------------------------------------------------------------------------------------------|

| 0 OBE |          | R   | 选项字节错误(Option Byte Error)  1: 所加载的选项字节和它的补码不匹配,选项字节和它的补码 强制写入 0xFF                                         |

| 2:1   | READPROT | R   | 读保护(Read Protect)<br>显示使能了哪个等级的读保护。<br>bit1 置一时即为等级 1, bit2 置一时即为等级 2。<br>00: 等级 0<br>01: 等级 1<br>1X: 等级 2 |

| 7:3   | 保留       |     |                                                                                                            |

| 位/域   | 名称            | R/W | 描述                                                     |

|-------|---------------|-----|--------------------------------------------------------|

| 8     | WDTSEL        | R   | 选择看门狗(Watchdog Select) 0: 硬件看门狗 1: 软件看门狗               |

| 9     | RSTSTOP       | R   | 进入停机模式时产生复位(nReset in STOP Mode)<br>0: 产生<br>1: 不产生    |

| 10    | RSTSTDB       | R   | 进入待机模式时产生复位(nReset in STANDBY Mode)<br>0: 产生<br>1: 不产生 |

| 11    |               |     | 保留                                                     |

| 12    | nBOOT1        | R   | 配置 nBOOT1 模式(nBoot1 Mode Configure)                    |

| 13    | VDDAMONI      | R   | VDDA 电压监控(VDDA Monitor)                                |

| 14    | SRAMPARITY    | R   | SRAM 奇偶校验(SRAM Parity Check)                           |

| 15    | 保留            |     | 保留                                                     |

| 23:16 | DATA0 R Data0 |     | Data0                                                  |

| 31:24 | DATA1 R       |     | Data1                                                  |

### 3.6.8 写保护寄存器(FMC\_WRTPROT)

偏移地址: 0x20

复位值: 0xXXXX XXXX (复位值取决于选项字节中编程值)

| 位/域  | 名称      | R/W | 描述                                   |

|------|---------|-----|--------------------------------------|

| 31:0 | WRTPROT | R   | 写保护(Write Protect)<br>0: 有效<br>1: 无效 |

### 4 系统配置控制器 (SYSCFG)

### 4.1 术语全称、缩写描述

表格 14 术语全称、缩写描述

| 中文全称    | 英文全称                            | 英文缩写   |

|---------|---------------------------------|--------|

| 超快模式    | Fast Mode Plus                  | FM+    |

| 系统配置控制器 | System Configuration Controller | SYSCFG |

SYSCFG 主要用于管理地址映射和控制中断,具体是指:控制部分 IO 口上的 I2C 的超快模式; TMR16, TMR17, USART1 和 ADC 的 DMA 触发源的重映射:存储器到代码起始区的重映射:管理连接到 GPIO 的外部中断。

有关配置的详情请见 SYSCFG 寄存器配置。

### 4.2 寄存器地址映射

表格 15 SYSCFG 寄存器地址映射

| 寄存器名            | 描述        | 偏移地址 |

|-----------------|-----------|------|

| SYSCFG_CFG1     | 配置寄存器 1   | 0x00 |

| SYSCFG_EINTCFG1 | 外部中断寄存器 1 | 0x08 |

| SYSCFG_EINTCFG2 | 外部中断寄存器 2 | 0x0C |

| SYSCFG_EINTCFG3 | 外部中断寄存器 3 | 0x10 |

| SYSCFG_EINTCFG4 | 外部中断寄存器 4 | 0x14 |

| SYSCFG_CFG2     | 配置寄存器 2   | 0x18 |

### 4.3 寄存器功能描述

### 4.3.1 配置寄存器 1 (SYSCFG CFG1)

配置内存和 DMA 请求的重映射 。

控制特定 I/O 引脚。

两位用来配置地址为 0x0000 0000 的存储类型。

这些位全部都可以跳过硬件由软件选择物理映射,且可以通过软件进行控制和复位。

复位后,这些位通过 BOOT 引脚选择模式配置参数。

偏移地址: 0x00

复位值: 0x0000 000X (X 指存储器模式,由 BOOT 控制)

| 位/域   | 名称              | R/W | 描述                                                                                                                                                                        |  |

|-------|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1:0   | MMSEL           | R/W | 存储映射选择(Memory Mapping Select)<br>控制内存映射地址 0x0000 0000。重置后这些位的参数由实际<br>BOOT 决定。<br>X0: 主闪存映射地址: 0x0000 0000<br>01: 系统闪存映射地址: 0x0000 0000<br>11: 嵌入式 SRAM 映射地址: 0x0000 0000 |  |

| 7:2   |                 | ·   | 保留                                                                                                                                                                        |  |

| 8     | ADCDMARMP       | R/W | ADC DMA 请求重映射(ADC DMA Request Remap)<br>控制 ADC DMA 的重映射请求。<br>0: 无重映射<br>ADC—DMA_CH1<br>1: 重映射<br>ADC—DMA CH2                                                             |  |

| 9     | USART1TXRMP     | R/W | USART1_TX DMA 请求重映射(USART1_TX DMA Request Remap)<br>该位控制 USART1_TX DMA 的重映射请求。<br>0: 无重映射<br>USART1_RX—DMA_CH2<br>1: 重映射<br>USART1 RX—DMA_CH4                             |  |

| 10    | USART1RXRMP     | R/W | USART1_RX DMA 请求重映射 (USART1_RX DMA Request Remap) 该位控制 USART1_RX DMA 的重映射请求。 0: 无重映射     USART1_TX—DMA_CH3 1: 重映射     USART1_TX—DMA_CH5                                   |  |

| 11    | TMR16DMARMP R/V |     | TMR16 DMA 请求重映射(TMR16 DMA Request Remap)<br>该位控制 TMR16 DMA 的重映射请求。<br>0: 无重映射<br>TMR16_CH1 和 TMR16_UP—DMA_CH3<br>1: 重映射<br>TMR16_CH1 和 TMR16_UP—DMA_CH4                   |  |

| 12    | TMR17DMARMP     | R/W | TMR17 DMA 请求重映射(TMR17 DMA Request Remap)<br>该位控制 TMR17 的重映射请求。<br>0: 无重映射<br>TMR17_CH1 和 TMR17_UP—DMA_CH1<br>1: 重映射<br>TMR17_CH1 和 TMR17_UP—DMA_CH2                       |  |

| 15:13 | 保留              |     |                                                                                                                                                                           |  |

| 16    | I2CPB6FMP       | R/W | 激活 PB6 引脚超快模式 (FM+) 驱动能力 (Fast Mode Plus Driving Capability Activate for PB6) 该位使能 PB6 接口开启 I2C 超快模式。 0: PB6 引脚被设置为标准模式。 1: PB6 引脚被设置为 I2C 超快模式,且 I2C 速度控制被旁路(被忽略)。       |  |

| 位/域   | 名称            | R/W | 描述                                                                                                                                                                    |

|-------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17    | I2CPB7FMP     | R/W | 激活 PB7 引脚超快模式 (FM+) 驱动能力 (Fast Mode Plus Driving Capability Activate for PB7) 该位使能 PB7 接口开启 I2C 超快模式。  0: PB7 引脚被设置为标准模式。  1: PB7 引脚被设置为 I2C 超快模式,且 I2C 速度控制被旁路(被忽略)。 |

| 18    | I2CPB8FMP     | R/W | 激活 PB8 引脚超快模式 (FM+) 驱动能力(Fast Mode Plus Driving Capability Activate for PB8) 该位使能 PB8 接口开启 I2C 超快模式。 0: PB8 引脚被设置为标准模式。 1: PB8 引脚被设置为 I2C 超快模式,且 I2C 速度控制被旁路(被忽略)。    |

| 19    | I2CPB9FMP R/W |     | 激活 PB9 引脚超快模式 (FM+) 驱动能力(Fast Mode Plus Driving Capability Activate for PB9) 该位使能 PB9 接口开启 I2C 超快模式。 0: PB9 引脚被设置为标准模式。 1: PB9 引脚被设置为 I2C 超快模式,且 I2C 速度控制被旁路(被忽略)。    |

| 20    | I2C1FMP       | R/W | 激活 I2C1 超快模式 (FM+) 驱动能力 (FM+ Driving Capability Activate for I2C1)  0: 超快模式只受 I2CPxxFM+位控制。  1: 超快模式可以选择 I2C1 的所有引脚,由 GPIO_AFx 选择。                                    |

| 21    | 保留            |     |                                                                                                                                                                       |

| 23:22 | I2CFMP        | R/W | 激活 I2C PA 引脚超快模式 (FM+) 驱动能力 (Fast Mode Plus Driving Capability Activate for I2C PA9 and PA10) 使能 PA9 和 PA10 引脚的超快模式。  0: PAx 引脚处于待机模式。  1: 使能,且速度控制被旁路(忽视)            |

| 31:24 | 保留            |     |                                                                                                                                                                       |

# 4.3.2 外部中断寄存器 1(SYSCFG\_EINTCFG1)

这些位由软件控制进行改写来选择 EINTx(x=0...3)的外部中断源。EINTx [3:0]的 值所代表选择的外部中断源如下表所示。

表格 16 不同值所选择外部中断源

| EINTx [3:0] | 外部中断源    |

|-------------|----------|

| x000        | PA[x] 引脚 |

| x001        | PB[x] 引脚 |

| x010        | PC[x] 引脚 |

| x011        | PD[x] 引脚 |

| x100        | 保留       |

| x101        | PF[x] 引脚 |

| 其他          | 保留       |

偏移地址: 0x08 复位值: 0x0000

| 位/域   | 名称    | R/W | 描述                                                                                       |

|-------|-------|-----|------------------------------------------------------------------------------------------|

| 3:0   | EINT0 | R/W | EINT 0 配置位(EINTO Configure)<br>这些位由软件控制进行改写来选择 EINTO 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。 |

| 7:4   | EINT1 | R/W | EINT1 配置位(EINT1 Configure)<br>这些位由软件控制进行改写来选择 EINT1 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。  |

| 11:8  | EINT2 | R/W | EINT2 配置位(EINT2 Configure)<br>这些位由软件控制进行改写来选择 EINT2 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。  |

| 15:12 | EINT3 | R/W | EINT3 配置位(EINT3 Configure)<br>这些位由软件控制进行改写来选择 EINT3 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。  |

| 31:16 | 保留    |     |                                                                                          |

### 4.3.3 外部中断寄存器 2(SYSCFG\_EINTCFG2)

这些位由软件控制进行改写来选择 EINTx(x=4...7)的外部中断源。EINTx [3:0]的 值所代表选择的外部中断源如表格 16 所示。

偏移地址: 0x0C 复位值: 0x0000

| 位/域   | 名称    | R/W | 描述                                                                                       |

|-------|-------|-----|------------------------------------------------------------------------------------------|

| 3:0   | EINT4 | R/W | EINT 4 配置位(EINT4 Configure)<br>这些位由软件控制进行改写来选择 EINT4 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。 |

| 7:4   | EINT5 | R/W | EINT5 配置位(EINT5 Configure)<br>这些位由软件控制进行改写来选择 EINT5 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。  |

| 11:8  | EINT6 | R/W | EINT6 配置位(EINT6 Configure)<br>这些位由软件控制进行改写来选择 EINT6 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。  |

| 15:12 | EINT7 | R/W | EINT7 配置位(EINT7 Configure)<br>这些位由软件控制进行改写来选择 EINT7 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。  |

| 31:16 |       |     | 保留                                                                                       |

### 4.3.4 外部中断寄存器 3(SYSCFG\_EINTCFG3)

这些位由软件控制进行改写来选择 EINTx(x=8...11)的外部中断源。EINTx [3:0]的 值所代表选择的外部中断源如表格 16 所示。

偏移地址: 0x10 复位值: 0x0000

| 位/域   | 名称     | R/W | 描述                                                                                         |

|-------|--------|-----|--------------------------------------------------------------------------------------------|

| 3:0   | EINT8  | R/W | EINT8 配置位(EINT8 Configure)<br>这些位由软件控制进行改写来选择 EINT8 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。    |

| 7:4   | EINT9  | R/W | EINT9 配置位(EINT9 Configure)<br>这些位由软件控制进行改写来选择 EINT9 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。    |

| 11:8  | EINT10 | R/W | EINT10 配置位(EINT10 Configure)<br>这些位由软件控制进行改写来选择 EINT10 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。 |

| 15:12 | EINT11 | R/W | EINT11 配置位(EINT11 Configure)<br>这些位由软件控制进行改写来选择 EINT11 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。 |

| 31:16 |        |     | 保留                                                                                         |

### 4.3.5 外部中断寄存器 4(SYSCFG\_EINTCFG4)

这些位由软件控制进行改写来选择 EINTx(x=12 to 15)的外部中断源。EINTx [3:0] 的值所代表选择的外部中断源如表格 16 所示。

偏移地址: 0x14 复位值: 0x0000

| 位/域   | 名称     | R/W | 描述                                                                                          |

|-------|--------|-----|---------------------------------------------------------------------------------------------|

| 3:0   | EINT12 | R/W | EINT 12 配置位(EINT12 Configure)<br>这些位由软件控制进行改写来选择 EINT12 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。 |

| 7:4   | EINT13 | R/W | EINT13 配置位(EINT13 Configure)<br>这些位由软件控制进行改写来选择 EINT13 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。  |

| 11:8  | EINT14 | R/W | EINT14 配置位(EINT14 Configure)<br>这些位由软件控制进行改写来选择 EINT14 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。  |

| 15:12 | EINT15 | R/W | EINT15 配置位(EINT15 Configure)<br>这些位由软件控制进行改写来选择 EINT15 的外部中断源。<br>位的值所表示选择的外部中断源如表格 16 所示。  |

| 31:16 |        |     | 保留                                                                                          |

# 4.3.6 配置寄存器 2 (SYSCFG\_CFG2)

偏移地址: 0x18 复位值: 0x0000

| 位/域 | 名称   | R/W | 描述                                                                                                                                                                 |

|-----|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | LOCK | R/W | 使能内核 LOCKUP(Core LOCKUP Enable)<br>该位由软件置位,由系统复位清除。<br>它可以使能和锁定 Arm <sup>®</sup> Crotex <sup>®</sup> -M0+ LOCKUP 的 Hardfault(硬件<br>错误)输出与 TMR1/15/16/17 刹车输入之间的连接。 |

| 位/域  | 名称                                                                                                                             | R/W | 描述                                                                                                            |  |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------|--|

| 1    | SRAMLOCK                                                                                                                       | R/W | 锁定 SRAM 校验(SRAM Parity Check Lock)<br>该位由软件置位,由系统复位实现清除。<br>能够使能和锁定 SRAM 奇偶错误信号与 TMR1/15/16/17 刹车输入<br>之间的连接。 |  |

| 7:2  | 保留                                                                                                                             |     |                                                                                                               |  |

| 8    | SRAM 校验标志(SRAM Parity Error Flag)<br>当检测到一个 SRAM 奇偶校验错误时,该位由硬件置位。<br>软件写入"1"时清除该位。<br>0: 没有检测到 SRAM 奇偶校验位错误<br>1: SRAM 奇偶校验位错误 |     | 当检测到一个 SRAM 奇偶校验错误时,该位由硬件置位。<br>软件写入"1"时清除该位。<br>0:没有检测到 SRAM 奇偶校验位错误                                         |  |

| 31:9 | 保留                                                                                                                             |     |                                                                                                               |  |

# 5 复位与时钟管理(RCM)

### 5.1 术语全称、缩写描述

表格 17 术语全称、缩写描述

| 中文全称    | 英文全称                       | 英文缩写   |

|---------|----------------------------|--------|

| 复位与时钟管理 | Reset and Clock Management | RCM    |

| 复位      | Reset                      | RST    |

| 上电复位    | Power-On Reset             | POR    |

| 掉电复位    | Power-Down Reset           | PDR    |

| 高速外部时钟  | High Speed External Clock  | HSECLK |

| 低速外部时钟  | Low Speed External Clock   | LSECLK |

| 高速内部时钟  | High Speed Internal Clock  | HSICLK |

| 低速内部时钟  | Low Speed Internal Clock   | LSICLK |

| 锁相环     | Phase Locked Loop          | PLL    |

| 主要时钟输出  | Main clock output          | MCO    |

| 校准      | Calibrate                  | CAL    |

| 调整      | Trim                       | TRM    |

| 时钟安全系统  | Clock Security System      | CSS    |

| 不可屏蔽中断  | Non Maskable Interrupt     | NMI    |

# 5.2 复位功能描述

支持的复位分为三类:系统复位、电源复位、RTC 区域复位三种复位形式。

### 5.2.1 系统复位

### 5.2.1.1 "系统复位"复位源

复位源可以分为外部复位源和内部复位源。

外部复位源:

● NRST 引脚上的低电平

内部复位源:

- 窗口看门狗终止计数(WWDT 复位)

- 独立看门狗终止计数(IWDT 复位)

- 软件复位(SW 复位)

- 低功耗管理复位

- 载入选项字节复位

#### ● 电源复位

以上任一事件发生时,都能产生一个系统复位。另外,可以通过查看 RCM CSTS(控制/状态寄存器)中的复位标志位识别复位事件来源。

一般来说,系统复位时,会将除了 RCM\_CSTS 的复位标志位以外的所有寄存器 的值复位到复位值。

### 软件复位

将 Arm® Cortex®-M0+中断应用和复位控制寄存器中的 SYSRESETREQ 置"1"时,可实现软件复位。

#### 低功耗管理复位

在以下两种情况下会产生低功耗管理复位,一种是进入待机模式时,另一种是进入停止模式时。在这两种情况下,如果把用户选择字节中的 RSTSTDB 位(待机模式时)或 RSTSTOP 位(停止模式时)清零,系统将被复位而不是进入待机模式或停止模式。

有关用户选择字节的详细信息,请参考"Flash 存储器"章节。

#### 载入选项字节复位

载入字节复位由被软件控制的在 FMC CTRL2 寄存器中 OBLOAD 位触发。

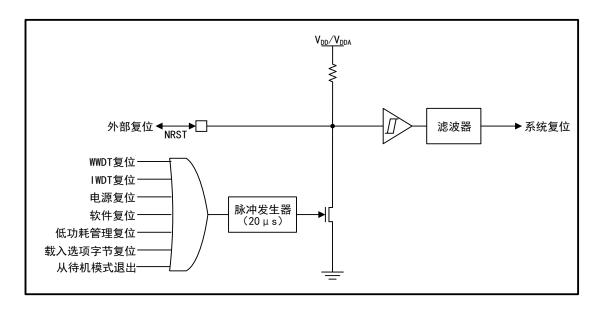

### 5.2.1.2 "系统复位"复位电路

复位源均作用于 NRST 引脚,该引脚并在复位过程中保持低电平。

内部复位源通过脉冲发生器在 NRST 引脚产生延时至少 20 µs 的脉冲,引起 NRST 保持电平产生复位;外部复位源则直接将 NRST 引脚电平拉低产生复位。

"系统复位"复位电路见下图。

### 图 2 "系统复位"复位电路

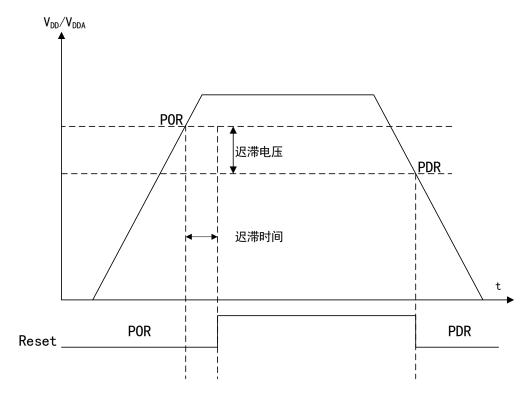

### 5.2.2 电源复位

"电源复位"复位源如下:

- 上电 (POR 复位)

- 掉电复位 (PDR 复位)

- 从待机模式唤醒

以上任一事件发生时,产生电源复位。

电源复位将复位所有寄存器。

### 5.2.3 RTC 域复位

"RTC 域复位"复位源如下:

- 置位 RCM RTCCTRL 中的 RTCRST 位触发的软件复位

- 上电复位 (POR 复位)

以上任一事件发生时,产生 RTC 域复位。

RTC 区域复位只影响 LSECLK 振荡器、RTC 实时时钟和寄存器 RCM\_RTCCTRL。

### 5.3 时钟管理功能描述

整个系统的时钟源有: HSECLK、LSECLK、HSICLK、HSICLK14、LSICLK、PLL。关于时钟源的特性,请参考数据手册的"电气特性"中的相关章节。

### 5.3.1 外部时钟源

外部时钟信号包括 HSECLK(高速外部时钟信号)和 LSECLK(低速外部时钟信号)。

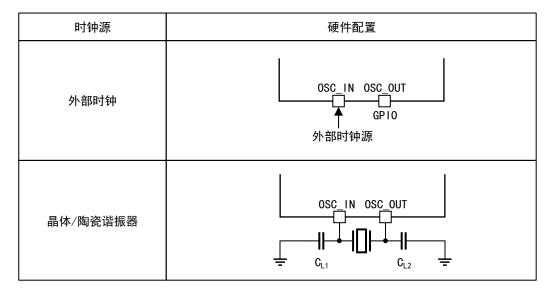

外部的时钟源有两种:

- 外部晶体/陶瓷谐振器

- 用户外部时钟

两种时钟源的硬件配置如下图所示。

图 3 HSECLK/LSECLK 的时钟源硬件配置

#### 注意:

- (1) 根据所选择的振荡器来调整负载电容(CL1、CL2)的值。

- (2) 为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容器必须尽可能 地靠近振荡器引脚。

### 5.3.1.1 HSECLK 高速外部时钟信号

HSECLK 时钟信号由 HSECLK 外部晶体/陶瓷谐振器和 HSECLK 外部时钟两种时钟源产生。

表格 18 产生 HSECLK 的时钟源

| 名称                        | 说明                                                                                                                                                                                                                                                     |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 外部时钟源<br>(HSECLK 旁路)      | 通过 OSC_IN 引脚给 MCU 提供时钟。<br>信号可以有普通的函数信号发送器(调试时)、晶体振荡器、其它信号发生器产生;波形可以是 40%-60%占空比的方波、正弦波或三角波,最高频率可达 32MHz。<br>硬件连接上,需连接必须连到 OSC_IN 引脚,同时保证 OSC_OUT 引脚悬空; MCU 配置上,用户可通过设置在 RCM_CTRL1 (时钟控制寄存器 1) 中的 HSEBCFG 和 HSEEN 位来选择这一模式。                            |

| 外部晶体/陶瓷谐振器<br>(HSECLK 晶体) | 通过谐振器给 MCU 提供时钟,谐振器包括晶体谐振器、陶瓷谐振器。频率范围是 4-32MHz。 需要 OSC_IN、OSC_OUT 连接谐振器,可以通过设置时钟控制寄存器 里 RCM_CTRL1(时钟控制寄存器)中的 HSEEN 位,启动和关闭。在时钟控制寄存器 RCM_CTRL1(时钟控制寄存器 1)中的 HSERDYFLG 位用来指示高速外部振荡器是否稳定。在启动后,直到这一位被硬件置"1",时钟才被释放出来。如果在 RCM_INT(时钟中断寄存器)中允许产生中断,将会产生相应中断。 |

#### 5.3.1.2 LSECLK 低速外部时钟信号

LSECLK 时钟信号由 LSECLK 外部晶体/陶瓷谐振器和 LSECLK 外部时钟两种时钟源产生。

表格 19 产生 LSECLK 的时钟源

| 名称                        | 说明                                                                                                                                                                                                                           |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 外部时钟源<br>(LSECLK 旁路)      | 通过 OSC32_IN 引脚给 MCU 提供时钟。信号可以有普通的函数信号发送器(调试时)、晶体振荡器、其它信号发生气产生;波形可以是 50%占空比的方波、正弦波或三角波,信号频率需为32.768kHz。硬件连接上,需连接必须连到 OSC32_IN 引脚,同时保证 OSC32_OUT 引脚悬空;MCU 配置上,用户可通过设置在 RCM_RTCCTRL 里的 LSEBCFG 和LSEEN 位来选择这个模式。                 |

| 外部晶体/陶瓷谐振器<br>(LSECLK 晶体) | 通过谐振器给 MCU 提供时钟,谐振器包括晶体谐振器、陶瓷谐振器。 频率是 32.768kHz。 需要 OSC32_IN、OSC32_OUT 连接谐振器,可以通过在 RCM_RTCCTRL 里的 LSEEN 位启动和关闭。 在 RCM_RTCCTRL 里的 LSERDYFLG 指示 LSECLK 晶体振荡是否稳定。在启动阶段,直到这个位被硬件置"1"后,LSECLK 时钟信号才被释放出来。 如果在时钟中断寄存器里被允许,可产生中断申请。 |

### 5.3.2 内部时钟源

内部时钟包含 HSICLK (高速内部时钟信号) 和 LSICLK (低速内部时钟信号)。

#### 5.3.2.1 HSICLK 高速内部时钟信号

HSICLK 时钟信号由内部 8MHz 的 RC 振荡器产生。

不同芯片的 RC 振荡器频率不同,且同一颗芯片随着温度、电压的变化也会存在差异,每个芯片的 HSICLK 时钟频率在出厂前已经被厂家校准到 1%(25℃、VDD=VDDA=3.3V),系统复位时,工厂校准值被装载到 RCM\_CTRL1(时钟控制寄存器)中,另外,用户可以依据现场的应用环境(温度、电压),通过设置RCM\_CTRL1中的 HSITRM 作进一步的频率调整。

HSIRDYFLG 位可以用来指示 HSICLK RC 振荡器是否稳定。在时钟启动过程中,直到 HSIRDYFLG 位被硬件置"1",HSICLK RC 输出时钟才被释放。 HSICLK RC 振荡器可由 RCM CTRL1 中的 HSIEN 位来启动或关闭。

与 HSECLK 晶体振荡器相比, RC 振荡器能够在不需要任何外部器件的条件下提供系统时钟;它的启动时间比 HSECLK 晶体振荡器短;即使在校准之后,其时钟频率精度仍不如 HSECLK 晶体振荡器。

#### 5.3.2.2 LSICLK 低速内部时钟信号

#### LSICLK 主要特征

LSICLK 由 RC 振荡器产生,范围是 40kHz(30kHz 和 60kHz 之间。随着温度、电压的变化,频率也会产生变化。可以在停机和待机模式下保持运行,为 IWDT(独立看门狗)和 RTC(实时时钟)提供时钟。

LSICLK 可以通过 RCM\_CSTS(控制/状态寄存器)的 LSIEN 位来启动或关闭。在 RCM\_CSTS 里的 LSIRDYFLG 位指示低速内部振荡器是否稳定。在启动阶段,直到这个位被硬件设置为"1"后,时钟才被释放。如果在 RCM\_INT(时钟中断寄存器)里被允许,将产生 LSICLK 中断申请。

### 5.3.3 PLL 锁相环

内部 PLL 可以用来倍频 HSICLK 的输出时钟或 HSECLK 晶体输出时钟。

如果要配置 PLL 参数,先将 PLLEN 位清 0,等到 PLLRDYFLG 被清 0(PLL 处于停用状态),然后改变参数,再将 PLLEN 置 1 通过使能 PLL,等 PLLRDYFLG 被置 1 即可完成配置。

时钟源和倍频因子应在被激活前完成选择,一旦 PLL 被激活,选择将不能改变。

当 PLL 准备就绪且 PLL 中断在 RCM\_INT 里被允许时,PLL 可发出中断申请。

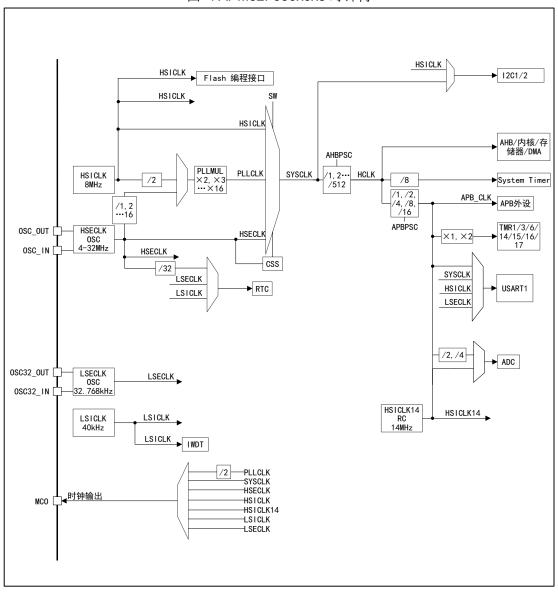

### 5.3.4 时钟树

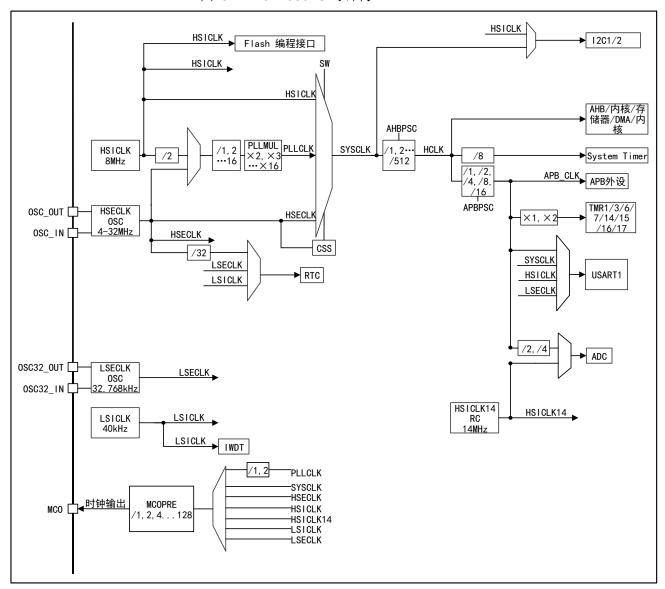

图 4 APM32F030x6x8 时钟树

#### 图 5 APM32F030xC 时钟树

#### 注意:

- (1) HCLK 是指 AHB 时钟。

- (2) PCLK 是指连接 APB 的外设的时钟信号。

- (3) FCLK 是 Arm® Cortex®-M0+的运行时钟。

- (4) 可通过多个预分频器配置 AHB、APB2(高速 APB)和 APB1(低速 APB)域的频率

- (5) 当需要运行连接 AHB, APB 的外设时,都需要开启相应的使能端,使外设获得时钟信号。

- (6) 所有 TMRxCLK(定时器时钟)频率分配由硬件按以下 2 种情况自动设置:

- 如果相应的 APB 预分频系数是 1,定时器的时钟频率与所在 APB 总线频率一致。

- 否则, 定时器的时钟频率被设为与其相连的 APB 总线频率的 2 倍。

- (7) 其中, TMRx (x=1,3,6,14,15,16,17) 时钟信号通过 APB 分频。

#### 5.3.5 RTC 的时钟源选择

通过设置 RCM\_RTCCTRL 的 RTCSRCSEL 位选择 HSECLK/32、LSECLK 或 LSICLK 作为 RTCCLK 时钟源。只有 RTC 域复位时,时钟源的选择才可以改变。只有当 PCLK 大于等于 RTCCLK 时,系统才能对 RTC 进行正常操作。

#### 5.3.6 IWDT 的时钟源选择

当 IWDT(独立看门狗)启动时,LSICLK 振荡器将被强制打开,等到稳定后把时钟信号供给 IWDT。LSICLK 在被强制打开后,将一直处于打开状态,不能被关闭。

#### 5.3.7 MCO 的时钟源选择

当相应的 GPIO 端口寄存器被配置为对应功能时,可通过配置 RCM\_CFG1 (时钟配置寄存器) 中的 MCOSEL 选择时钟信号输出到 MCO 引脚。具体时钟信号可参考时钟树或 RCM\_CFG1 寄存器的 MCOSEL 位说明。

#### 5.3.8 SYSCLK 的时钟源选择

SYSCLK 时钟源可以是 HSECLK、PLLCLK 或 HSICLK。

RCM CFG1 的状态位可指示已准备好的时钟和已被选作的 SYSCLK 时钟源。

当进行系统复位后,HSICLK 振荡器被选作系统时钟,且当 PLL 直接或间接作为系统时钟时,该时钟源不能被停止。如果要切换 SYSCLK 时钟源,必须要等目标时钟源准备就绪(即目标时钟源稳定)。

### 5.3.9 CSS 时钟安全系统

为了防止由于外部晶振短路导致 MCU 无法正常运行的情况,MCU 可通过软件激活 CSS 时钟安全系统。安全系统被激活后,如果 HSECLK 振荡器直接或间接(作为 PLL 输入时钟且 PLL 作为系统时钟)被用作系统时钟,那么当 HSECLK 时钟发生故障时,外部 HSECLK 振荡器被关闭,系统时钟自动切换至 HSICLK,此时选择 HSECLK 为时钟输入且作为系统时钟输入源的 PLL 也会被关闭。

可通过软件激活 CSS,当 HSECLK 时钟出现故障时,产生 CSS 中断,并且 NMI 也自动产生。NMI 将被不断执行,直到 CSS 中断挂起位被清除。因此,在 NMI 的处理程序中必须通过设置 RCM\_INT(时钟中断寄存器)里的 CSSCLR 位来清除 CSS 中断。

#### 5.3.10 ADC 的时钟源选择

ADC 的时钟源通过 ADC\_CFG2 控制。它能够选择 HSICLK14 或被 2/4 分频的 PCLK 作为时钟源。当 PCLK 作为 ADC 的时钟源时,HSICLK14 无法转接到 ADC 接口。

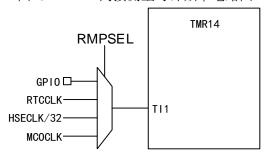

#### 5.3.11 基于 TMR14 的内/外部时钟测量

通过 TMR14 通道 1 的输入捕获功能,可以间接测量主板上的所有时钟源发生器的频率,电路图如下所示:

图 6 TMR14 间接测量时钟频率电路图

TMR14 的输入捕获可以选择通过配置 TMR14 的 TMRx\_OPT 寄存器的 RMPSEL 位,连接一个 GPIO 端口或一个 MCU 的内部时钟(RTCCLK,HSECLK/32,MCOCLK)。具体配置见该寄存器。

#### 5.3.12 低功耗模式

PCLK 和 DMACLK 可以用软件禁止。

#### 睡眠模式:

- 停止 CPU 时钟

- 可软件停止 Flash 和 RAM 接口时钟

- 所有连接 APB 总线的外设时钟被禁止时,硬件停止 AHB1/APB 桥时钟

#### 停止模式和待机模式:

- 禁止所有 1.5V 电源域

- 禁止 PLLCLK、HSICLK、HSICLK14 和 HSECLK

#### 深度睡眠模式:

- 通过设置 DBGMCU\_CFG 中的 STOP\_CLK\_STS 位和 STANDBY CLK STS 位,可以对系统进行调试

- 系统通过中断(停止模式)或复位(待机模式)选择 HSICLK 作为 SYSCLK

- 如果正在进行 Flash 编程,则在完成所有编程操作后才会进入深度睡眠模式

- 如果正在使用 APB 域,则在完成所有操作后才会进入深度睡眠模式

### 5.4 寄存器地址映射

表格 20 RCM 寄存器地址映射

| 寄存器名         | 描述            | 偏移地址 |

|--------------|---------------|------|

| RCM_CTRL1    | 时钟控制寄存器 1     | 0x00 |

| RCM_CFG1     | 时钟配置寄存器 1     | 0x04 |

| RCM_INT      | 时钟中断寄存器       | 0x08 |

| RCM_APBRST2  | APB2 外设复位寄存器  | 0x0C |

| RCM_APBRST1  | APB1 外设复位寄存器  | 0x10 |

| RCM_AHBCLKEN | AHB 外设时钟使能寄存器 | 0x14 |

| 寄存器名          | 描述             | 偏移地址 |

|---------------|----------------|------|

| RCM_APBCLKEN2 | APB2 外设时钟使能寄存器 | 0x18 |

| RCM_APBCLKEN1 | APB1 外设时钟使能寄存器 | 0x1C |

| RCM_RTCCTRL   | RTC 域控制寄存器     | 0x20 |

| RCM_CSTS      | 控制/状态寄存器       | 0x24 |

| RCM_IORST     | I/O 引脚复位寄存器    | 0x28 |

| RCM_CFG2      | 时钟配置寄存器 2      | 0x2C |

| RCM_CFG3      | 时钟配置寄存器 3      | 0x30 |

| RCM_CTRL2     | 时钟控制寄存器 2      | 0x34 |

# 5.5 寄存器功能描述

# 5.5.1 时钟控制寄存器 1(RCM\_CTRL1)

偏移地址: 0x00

复位值: 0x0000 XX83, X 代表未定义

访问: 以字,半字和字节形式访问, 无等待周期

| 位/域  | 名称        | R/W | 描述                                                                                                                                                                                                                                     |

|------|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | HSIEN     | R/W | 使能高速内部时钟(High Speed Internal Clock Enable)由软件置 1 或清 0。 HSICLK 是 RC 振荡器,以下条件中的一个出现时,会硬件置 1: 上电启动、软件复位、从待机模式唤醒、停机模式唤醒、外部高速时钟源(作为系统时钟或通过 PLL 提供系统时钟)发生故障。当 HSICLK 作为系统时钟源或通过 PLL 提供系统时钟时,该位不能清 0。 0: 关闭 HSICLK RC 振荡器 1: 开启 HSICLK RC 振荡器 |

| 1    | HSIRDYFLG | R   | 高速内部时钟就绪标志(High Speed Internal Clock Ready Flag)  0: HSICLK RC 振荡器未稳定  1: HSICLK RC 振荡器已稳定                                                                                                                                             |

| 2    |           |     | 保留                                                                                                                                                                                                                                     |

| 7:3  | HSITRM    | R/W | 调整高速内部时钟(High Speed Internal Clock Trim)<br>产品在出厂时会校准到 8MHz±1%,但随着温度、电压的变化而变化,<br>可通过 HSITRM[4:0]调整 HSICLK RC 振荡器的频率。                                                                                                                  |

| 15:8 | HSICAL    | R   | 校准内部高速时钟(High Speed Internal Clock Calibrate)<br>在出厂时会校准到 8MHz±1%,在系统启动时,会将校准参数自动写入<br>该寄存器。                                                                                                                                           |

| 16   | HSEEN     | R/W | 使能高速外部时钟(High Speed External Clock Enable)进入待机或停机模式时,该位由硬件清 0,关闭 HSECLK; 当 HSECLK 作为系统时钟源或通过 PLL 提供系统时钟时,该位不能清 0。 0: HSECLK 关闭 1: HSECLK 开启                                                                                            |

| 位/域   | 名称        | R/W | 描述                                                                                                                            |  |

|-------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------|--|

| 17    | HSERDYFLG | R   | 高速外部时钟就绪标志(High Speed External Clock Ready Flag)<br>HSECLK 稳定后有硬件置 1,软件清 0。<br>0: HSECLK 未稳定<br>1: HSECLK 已稳定                 |  |

| 18    | HSEBCFG   | R/W | 配置高速外部时钟旁路模式(High Speed External Clock Bypass Configure)<br>旁路模式指外部时钟作为 HSECLK 时钟源,否则谐振器作为 HSECLK 时钟源。<br>0: 非旁路模式<br>1: 旁路模式 |  |

| 19    | CSSEN     | R/W | 使能时钟安全系统(Clock Security System Enable)<br>0:禁止<br>1:使能                                                                        |  |

| 23:20 | 保留        |     |                                                                                                                               |  |

| 24    | PLLEN     | R/W | 使能 PLL (PLL Enable) 当进入待机和停止模式时,该位由硬件清零; 当 PLLCLK 已配置为(或者配置过程中)系统时钟的时钟源,该位不能清 0; 其他情况可由软件置 1 或清 0。 0: PLL 关闭 1: PLL 使能        |  |

| 25    | PLLRDYFLG | R   | PLL 时钟就绪标志(PLL Clock Ready Flag) PLL 锁定后由硬件置 1。 0: PLL 未锁定 1: PLL 锁定                                                          |  |

| 31:26 |           |     | 保留                                                                                                                            |  |

# 5.5.2 时钟配置寄存器 1 (RCM\_CFG1)

偏移地址: 0x04

复位值: 0x0000 0000

此寄存器所有位都由软件置位或清零。

访问: 以字,半字和字节形式访问,0到2个等待周期。

只有当访问发生在时钟切换时,才会插入1或2个等待周期。

| 位/域 | 名称         | R/W | 描述                                                                                                                                                                      |

|-----|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SCLKSEL    | R/W | 选择系统时钟时钟源(System Clock Source Select) 在从停止或待机模式中返回时或直接或间接作为系统时钟的 HSECLK 出现故障时,由硬件强制选择 HSICLK 作为系统时钟(如果时钟安全系统已经启动) 00: HSICLK 作为系统时钟 01: HSECLK 作为系统时钟 10: PLLCLK 作为系统时钟 |

| 3:2 | SCLKSELSTS | R   | 系统时钟时钟源选择状态(System Clock Selection Status)<br>指示哪一个时钟源被作为系统时钟;由硬件置 1 或清 0。<br>00:HSICLK 作为系统时钟<br>01:HSECLK 作为系统时钟                                                      |

| 位/域   | 名称           | R/W   | 描述                                                       |

|-------|--------------|-------|----------------------------------------------------------|

|       |              |       | 10: PLLCLK 输出作为系统时钟                                      |

|       |              |       | 11: 不可用                                                  |

|       |              |       | 配置 AHB 时钟预分频(AHB Clock Prescaler Factor Configure)       |

|       |              |       | 控制 AHB 时钟的预分频系数。                                         |

|       |              |       | 0xxx: SYSCLK 不分频                                         |

|       |              |       | 1000: SYSCLK 2 分频                                        |

|       |              |       | 1001: SYSCLK 4 分频                                        |

| 7:4   | AHBPSC       | R/W   | 1010: SYSCLK 8 分频                                        |

|       |              |       | 1011: SYSCLK 16 分频                                       |

|       |              |       | 1100: SYSCLK 64 分频                                       |

|       |              |       | 1101: SYSCLK 128 分频                                      |

|       |              |       | 1110: SYSCLK 256 分频<br>1111: SYSCLK 512 分频               |

|       |              |       | TITI: SYSOLK 512 分频                                      |

|       |              |       |                                                          |

|       |              |       | 配置 APB1 时钟预分频系数(APB1 Clock Prescaler Factor Configure)   |

|       |              |       | 来控制低速 APB1 时钟(PCLK1)的预分频系数。                              |

| 10.0  | ADD4D00      | D/\/  | 0xx: HCLK 不分频                                            |

| 10:8  | APB1PSC      | R/W   | 100: HCLK 2 分频                                           |

|       |              |       | 101: HCLK 4 分频                                           |

|       |              |       | 110: HCLK 8 分频<br>111: HCLK 16 分频                        |

| 14:11 |              |       | 保留                                                       |

| 14.11 |              | 1     |                                                          |

|       |              |       | 选择 PLL 时钟源(PLL Clock Source Select)                      |

|       |              |       | 只能在关闭 PLL 时才能改变此位。                                       |

|       |              |       | 对于 F030x6x8, bit15 无效, 为保留位, bit16 有效:                   |

|       |              |       | 0: HSICLK 2 分频后作为 PLL 时钟源                                |

| 16:15 | PLLSRCSEL    | R/W   | 1: HSECLK 作为 PLL 时钟源                                     |

|       |              |       |                                                          |

|       |              |       |                                                          |

|       |              |       |                                                          |

|       |              |       |                                                          |

|       |              |       |                                                          |

| 17    | PLI HSEPSC   | R/\/  |                                                          |

| .,    | . LLIIOLI OO | 17/// |                                                          |

|       |              |       | _                                                        |

|       |              |       | ·                                                        |

|       |              |       |                                                          |

|       |              |       |                                                          |

|       |              |       |                                                          |

| 21:18 | PLLMULCFG    | R/W   |                                                          |

| 21.10 | FLLWIOLOFG   |       | 0100: PLL 6 倍频输出                                         |

|       |              |       | 0101: PLL 7 倍频输出                                         |

|       |              |       | 0110: PLL 8 倍频输出                                         |

|       |              |       | 0111: PLL 9 倍频输出                                         |

|       |              |       | 1000: PLL 10 倍频输出                                        |

| 21:18 | PLLHSEPSC    | R/W   | 0101: PLL 7 倍频输出<br>0110: PLL 8 倍频输出<br>0111: PLL 9 倍频输出 |

| 位/域   | 名称        | R/W | 描述                                                       |

|-------|-----------|-----|----------------------------------------------------------|

|       |           |     | 1001: PLL 11 倍频输出                                        |

|       |           |     | 1010: PLL 12 倍频输出                                        |

|       |           |     | 1011: PLL 13 倍频输出                                        |

|       |           |     | 1100: PLL 14 倍频输出                                        |

|       |           |     | 1101: PLL 15 倍频输出                                        |

|       |           |     | 1110: PLL 16 倍频输出                                        |

|       |           |     | 1111: PLL 16 倍频输出                                        |

|       |           |     | 注意: PLL 的输出频率不能超过 48MHz。                                 |

| 23:22 |           |     | 保留                                                       |

|       |           |     | 选择主时钟输出(Main Clock Output Select)                        |

|       |           |     | 由软件置位或清零。                                                |

|       |           |     | 0000: 没有时钟输出                                             |

|       |           |     | 0001: HSICLK14 作为时钟输出                                    |

|       |           |     | 0010: LSICLK 作为时钟输出                                      |

| 27:24 | MCOSEL    | R/W | <b>0011: LSECLK</b> 作为时钟输出                               |

|       |           |     | 0100: SYSCLK 作为时钟输出                                      |

|       |           |     | 0101: HSICLK 作为时钟输出                                      |

|       |           |     | 0110: HSECLK 作为时钟输出                                      |

|       |           |     | 0111:PLLCLK经过2分频或者1分频后作为时钟输出(由PLLDIVCFG设置)               |

|       |           |     | 1xxx: 保留                                                 |

|       |           |     | 选择 MCO 预分频器分频系数(MCO Prescaler Division Factor Select)    |

|       |           |     | 这些位由软件设置和清除。为避免故障,建议仅在禁用 MCO 输出时更改此预分频器。(此位域仅适用于 F030xC) |

|       |           |     | 000: MCO 1 分频                                            |

| 30:28 | MCOPRESEL | R/W | 001: MCO 2 分频                                            |

|       |           |     | 010: MCO 4 分频                                            |

|       |           |     |                                                          |

|       |           |     | 111: MCO 128 分频                                          |

|       |           |     | 配置 MCO 锁相环时钟分频(MCO PLL Clock Frequency Division          |

|       |           |     | Configure )                                              |

| 31    | PLLDIVCFG | R/W | 该位由软件设置和清除。(此位域仅适用于 F030xC)                              |

|       |           |     | 0: MCO 的锁相环 2 分频                                         |

|       |           |     | 1: MCO 的锁相环 1 分频                                         |

## 5.5.3 时钟中断寄存器 (RCM\_INT)

偏移地址: 0x08 复位值: 0x0000 0000

访问: 以字,半字和字节形式访问, 无等待周期。

| 位/域 | 名称        | R/W | 描述                                                                                                                                         |

|-----|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | LSIRDYFLG | R   | LSICLK 就绪中断标志(LSICLK Ready Interrupt Flag) LSICLK 稳定且 LSIRDYEN 位被置 1 时,由硬件置 1; 由软件置 1 LSIRDYCLR 清 0 该位。 0: 无 LSICLK 就绪中断 1: 发生 LSICLK 就绪中断 |

| 位/域 | 名称          | R/W | 描述                                                                                                                                                                             |  |  |

|-----|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | LSERDYFLG   | R   | LSECLK 就绪中断标志(LSECLK Ready Interrupt Flag) LSECLK 稳定且 LSERDYEN 位被置 1 时,由硬件置 1;由软件置 1 LSERDYCLR 清 0 该位。 0:无 LSECLK 就绪中断 1:发生 LSECLK 就绪中断                                        |  |  |

| 2   | HSIRDYFLG   | R   | HSICLK 就绪中断标志(HSICLK Ready Interrupt Flag) HSICLK 稳定且 HSIRDYEN 位被置 1 时,由硬件置 1;由软件置 1 HSIRDYCLR 清 0 该位。 0:无 HSICLK 就绪中断 1:发生 HSICLK 就绪中断                                        |  |  |

| 3   | HSERDYFLG   | R   | HSECLK 就绪中断标志(HSECLK Ready Interrupt Flag) HSECLK 稳定且 HSERDYEN 位被置 1 时,由硬件置 1;由软件置 1 HSERDYCLR 清 0 该位。 0:无 HSECLK 就绪中断 1:发生 HSECLK 就绪中断                                        |  |  |

| 4   | PLLRDYFLG   | R   | PLL 就绪中断标志(PLL Ready Interrupt Flag) PLL 稳定且 PLLRDYEN 位被置 1 时,由硬件置 1;由软件置 1 PLLRDYCLR 清 0 该位。 0: 无 PLL 锁定产生的时钟就绪中断 1: 发生 PLL 锁定产生的时钟就绪中断                                       |  |  |

| 5   | HSI14RDYFLG | R   | HSICLK14 就绪中断标志(HSICLK14 Ready Interrupt Flag)<br>在内部高速时钟就绪且 HSI14RDYEN 位被置 1 时,由硬件置 1。<br>软件置 1HSI14RDYCLR 清 0 该位。<br>0: 无 HSI14CLK 失效产生的安全系统中断<br>1: 发生 HSI14CLK 失效产生的安全系统中断 |  |  |

| 6   | 保留          |     |                                                                                                                                                                                |  |  |

| 7   | CSSFLG      | R   | 时钟安全系统中断标志(Clock Security System Interrupt Flag)<br>在外部 4-16MHz 振荡器时钟出现故障时,由硬件置 1。<br>软件置 1CSSCLR 清 0 该位。<br>0: 无 HSECLK 时钟失效产生的安全系统中断<br>1: HSECLK 时钟失效导致了时钟安全系统中断            |  |  |

| 8   | LSIRDYEN    | R/W | 使能 LSICLK 就绪中断(LSICLK Ready Interrupt Enable)<br>使能或关闭内部 40KHz RC 振荡器就绪中断。<br>0: 禁止<br>1: 使能                                                                                   |  |  |

| 9   | LSERDYEN    | R/W | 使能 LSECLK 就绪中断(LSECLK Ready Interrupt Enable)<br>使能外部 32KHz RC 振荡器就绪中断。<br>0: 禁止<br>1: 使能                                                                                      |  |  |

| 10  | HSIRDYEN    | R/W | 使能 HSICLK 就绪中断(HSICLK Ready Interrupt Enable)<br>使能内部 8MHz RC 振荡器就绪中断。<br>0: 禁止<br>1: 使能。                                                                                      |  |  |

| 位/域   | 名称          | R/W | 描述                                                                                                      |

|-------|-------------|-----|---------------------------------------------------------------------------------------------------------|

| 11    | HSERDYEN    | R/W | 使能 HSCLKE 就绪中断(HSECLK Ready Interrupt Enable)<br>使能外部 4-16MHz 振荡器就绪中断。<br>0:禁止<br>1:使能                  |

| 12    | PLLRDYEN    | R/W | 使能 PLL 就绪中断(PLL Ready Interrupt Enable)<br>使能 PLL 就绪中断。<br>0:禁止<br>1:使能                                 |

| 13    | HSI14RDYEN  | R/W | 使能 HSICLK14 就绪中断(HSICLK14 Ready Interrupt Enable)<br>使能内部 14MHz RC 振荡器就绪中断。<br>0: 禁止<br>1: 使能。          |

| 15:14 |             |     | 保留                                                                                                      |

| 16    | LSIRDYCLR   | W   | 清除 LSICLK 就绪中断(LSICLK Ready Interrupt Clear)<br>清除 LSICLKI 就绪中断标志位 LSIRDYFLG。<br>0: 无作用<br>1: 清除        |

| 17    | LSERDYCLR   | W   | 清除 LSECLK 就绪中断(LSECLK Ready Interrupt Clear)<br>清除 LSECLK 就绪中断标志位 LSERDYFLG。<br>0: 无作用<br>1: 清除         |

| 18    | HSIRDYCLR   | W   | 清除 HSICLK 就绪中断(HSICLK Ready Interrupt Clear)<br>清除 HSI 就绪中断标志位 HSIRDYFLG。<br>0: 无作用<br>1: 清除            |

| 19    | HSERDYCLR   | W   | 清除 HSECLK 就绪中断(HSECLK Ready Interrupt Clear)<br>清除 HSE 就绪中断标志位 HSERDYFLG。<br>0: 无作用<br>1: 清除            |

| 20    | PLLRDYCLR   | W   | 清除 PLL 就绪中断(PLL Ready Interrupt Clear)<br>清除 PLL 就绪中断标志位 PLLRDYFLG。<br>0: 无作用<br>1: 清除                  |

| 21    | HSI14RDYCLR | W   | 清除 HSICLK14 就绪中断(HSICLK14 Ready Interrupt Clear)<br>清除 HSICLK14 就绪中断标志位 HSI14RDYFLG。<br>0: 无作用<br>1: 清除 |

| 22    | 保留          |     |                                                                                                         |

| 23    | CSSCLR      | W   | 清除时钟安全系统中断(Clock Security System Interrupt Clear)<br>清除安全系统中断标志位 CSSFLG。<br>0: 无作用<br>1: 清除             |

| 31:24 |             |     | 保留                                                                                                      |

## 5.5.4 APB 外设复位寄存器 2(RCM\_APBRST2)

偏移地址: 0x0C

复位值: 0x0000 0000

访问: 以字,半字和字节形式访问, 无等待周期。

所有位都可以由软件置位或清 0。

| 位/域   | 名称        | R/W | 描述                                           |  |  |

|-------|-----------|-----|----------------------------------------------|--|--|

| 0     | SYSCFGRST | R/W | 复位系统配置寄存器(SYSCFG Reset)<br>0: 无作用<br>1: 复位   |  |  |

| 4:1   |           |     | 保留                                           |  |  |

| 5     | USART6RST | R/W | 复位 USART6 (USART6 Reset) 0: 无作用 1: 复位 USART6 |  |  |

| 8:6   |           |     | 保留                                           |  |  |

| 9     | ADCRST    | R/W | 复位 ADC(ADC Reset) 0: 无作用 1: 复位 ADC           |  |  |

| 10    |           |     | 保留                                           |  |  |

| 11    | TMR1RST   | R/W | 复位 TMR1 定时器(TMR1 Timer Reset) 0: 无作用 1: 复位   |  |  |

| 12    | SPI1RST   | R/W | 复位 SPI1 (SPI1 Reset) 0: 无作用 1: 复位            |  |  |

| 13    | 保留        |     |                                              |  |  |

| 14    | USART1RST | R/W | 复位 USART1 (USART1 Reset) 0: 无作用 1: 复位        |  |  |

| 15    | 保留        |     |                                              |  |  |

| 16    | TMR15RST  | R/W | 复位 TMR15(TMR15 Reset)<br>0: 无作用<br>1: 复位     |  |  |

| 17    | TMR16RST  | R/W | 复位 TMR16 (TMR16 Reset) 0: 无作用 1: 复位          |  |  |

| 18    | TMR17RST  | R/W | 复位 TMR17 (TMR17 Reset) 0: 无作用 1: 复位          |  |  |

| 21:19 |           |     | 保留                                           |  |  |

| 22    | DBGRST    | R/W | 复位 Debug(Debug Reset)<br>0: 无作用<br>1: 复位     |  |  |

| 31:23 |           |     | 保留                                           |  |  |

## 5.5.5 APB 外设复位寄存器 1(RCM\_APBRST1)

偏移地址: 0x10

复位值: 0x0000 0000

访问: 以字,半字和字节形式访问, 无等待周期

| 位/域   | 名称        | R/W | 描述                                                |  |

|-------|-----------|-----|---------------------------------------------------|--|

| 0     |           | I   | 保留                                                |  |

| 1     | TMR3RST   | R/W | 复位定时器 3(Timer 3 Reset)<br>0: 无作用<br>1: 复位         |  |

| 3:2   |           | I   | 保留                                                |  |

| 4     | TMR6RST   | R/W | 复位定时器 6(Timer 6 Reset)<br>0: 无作用<br>1: 复位         |  |

| 5     | TMR7RST   | R/W | 复位定时器 7(Timer 7 Reset)<br>0: 无作用<br>1: 复位         |  |

| 7:6   |           |     | 保留                                                |  |

| 8     | TMR14RST  | R/W | 复位定时器 14(Timer14 Reset)<br>0: 无作用<br>1: 复位        |  |

| 10:9  | 保留        |     |                                                   |  |

| 11    | WWDTRST   | R/W | 复位窗口看门狗(Window Watchdog Reset)<br>0: 无作用<br>1: 复位 |  |

| 13:12 | 保留        |     |                                                   |  |

| 14    | SPI2RST   | R/W | 复位 SPI2(SPI2 Reset)<br>0: 无作用<br>1: 复位            |  |

| 16:15 |           |     | 保留                                                |  |

| 17    | USART2RST | R/W | 复位 USART2 (USART2 Reset) 0: 无作用 1: 复位             |  |

| 18    | USART3RST | R/W | 复位 USART3 (USART3 Reset) 0: 无作用 1: 复位             |  |

| 19    | USART4RST | R/W | 复位 USART4 (USART4 Reset) 0: 无作用 1: 复位             |  |

| 20    | USART5RST | R/W | 复位 USART5 (USART5 Reset) 0: 无作用 1: 复位             |  |

| 位/域   | 名称      | R/W  | z/W 描述                                 |  |  |  |

|-------|---------|------|----------------------------------------|--|--|--|

| 21    | I2C1RST | R/W  | 复位 I2C1 (I2C1 Reset) 0: 无作用 1: 复位      |  |  |  |

| 22    | I2C2RST | R/W  | 复位 I2C2(I2C2 Reset)<br>0: 无作用<br>1: 复位 |  |  |  |

| 27:23 |         | 保留   |                                        |  |  |  |

| 28    | PMURST  | JRST |                                        |  |  |  |

| 31:29 | 保留      |      |                                        |  |  |  |

## 5.5.6 AHB 外设时钟使能寄存器(RCM\_AHBCLKEN)

偏移地址: 0x14

复位值: 0x0000 0014

访问: 以字,半字和字节形式访问, 无等待周期

所有位都可以由软件置位或清 0。

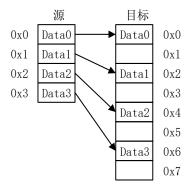

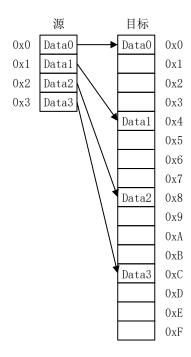

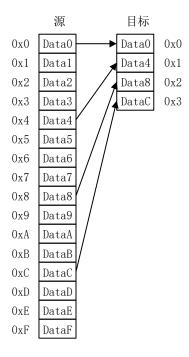

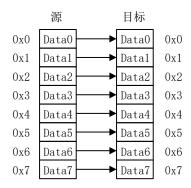

注:当外设时钟没有启用时,软件不能读出外设寄存器的数值,返回的数值始终是 0x0。